|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

abstract

コンピュータシステムの高性能化の歩みについて,プロセッサの高周波数化,メモリとのデータ転送の拡大,並列処理の三つの視点で振り返る.コンピュータのアーキテクチャやマイクロプロセッサの発展に対して半導体技術やエレクトロニクスがいかに貢献してきたかを概観する.

キーワード:プロセッサ,半導体,メモリ階層,マルチコア,スーパコンピュータ

コンピュータが電子計算機と呼ばれることがあるように,コンピュータシステムの実現とエレクトロニクス技術の革新は表裏一体である.最先端のエレクトロニクス技術を使って新たなコンピュータが開発され,高性能なコンピュータを実現するために新たなエレクトロニクス技術が開発されてきた.

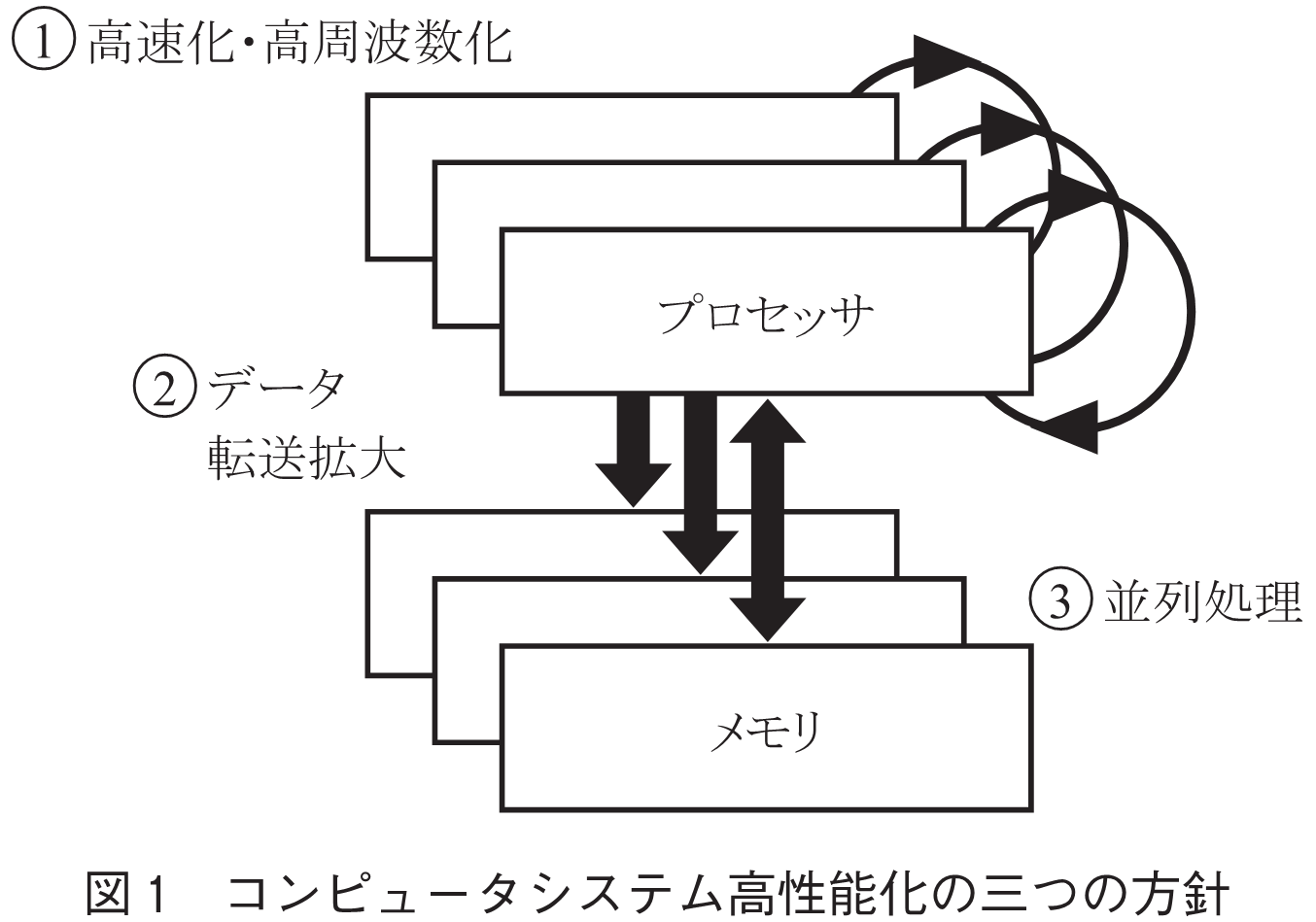

コンピュータシステムは,プログラムの命令を実行することでデータを処理するシステムである.エレクトロニクスは正にこの命令とデータの高速実行,高速処理を実現した.その活用方針は主に次の三つである(図1).

① 命令実行やデータ処理の高速化,高周波数化

② プロセッサとメモリの間のデータ転送拡大

③ プログラムの並列処理

エレクトロニクスは,電子回路の高速化,微細化,低電力化,そして低コスト化によってこれらの設計方針を実現してきた.例えば,真空管からトランジスタ,LSI(Large Scale Integration)へと回路素子が高速化,微細化することによって命令実行やデータ処理の高速化,高周波数化が可能になった.また,回路の高集積化によって命令実行のパイプライン処理やスーパスカラ,アウトオブオーダ,マルチスレッディングといった高度で複雑な並列処理が実現されるようになった.

プロセッサとメモリの間のデータ転送拡大については,DRAM(Dynamic Random Access Memory)のような外部メモリ・インタフェースの高速化と並んで,キャッシュメモリのようなプロセッサ内蔵メモリの高集積化,大容量化が大きく貢献している.

そしてハイエンドのコンピュータシステムで現在主流となっている大規模マルチコアコンピュータシステムに最先端のエレクトロニクス技術による高集積化と低電力化,そして総合的な低コスト化が不可欠であることは言うまでもない.

ここでは,その時代時代の最先端のコンピュータシステムの開発,コンピュータアーキテクチャの革新と実現に対してエレクトロニクス技術がどのように関わってきたかを振り返り,その意義を再確認する.

今はもはや歴史的な言い回しとなったが,第1世代のコンピュータは真空管を使ったコンピュータと定義された.第2世代はトランジスタを部品として作られ,第3世代は集積回路で作られたコンピュータである.どのようなエレクトロニクス技術を使ったかでコンピュータの世代が定義される時代があった.このようなコンピュータの世代認識の下に1976年に設立された超エル・エス・アイ技術研究組合が日本の半導体技術開発に大きく貢献したのもまた歴史の1ページである.

「超マシン誕生」(1)という本がある.Data GeneralのスーパミニコンピュータEclipse MV/8000の開発ドキュメンタリーで1982年のピューリツァ賞を受賞,DEC VAX11/780対抗で16ビットミニコンピュータNOVAの32ビット互換機Eagle(MV/8000のコード名)を新人主体のチームで開発するプロジェクト記録である.

Eagleのプロセッサは七つのボードに実装された.当時のエレクトロニクス技術では32ビットスーパミニコンピュータの機能を1チップに集積することはできなかった.一方,プロセッサを実現する回路素子としてディスクリートの演算チップとPAL(Programmable Array Logic)が採用された.初期の小規模なプログラマブルロジックデバイスである.これによって「設計の中のややこしい部分」に差し掛かったときに設計図に「単に四角を描き込み,その中を空白にしておくこと」ができた.短期間でのハードウェア設計,デバッグに有効に働いたことだろう.今ならFPGA(Field Programmable Gate Array)を使うところである.このようにコンピュータ開発では,当時も今も最新のエレクトロニクス技術の中から何を選んでコンピュータを開発するかが設計上で最も重要な決断であった.

背景として書かれているのがダウンサイジングである.1970年代後半から1980年代に掛けて,それまで16ビット処理だったミニコンピュータが32ビット化してIBMなどの大形コンピュータに基本処理性能で肩を並べた.そしてコストパフォーマンスでこれを凌駕し,コンピュータの小形化,パーソナル化の幕が開いた.大形コンピュータがより小形のコンピュータに置き換わり,価格の低下とともに市場拡大,パーソナル化が進むというダウンサイジングは半導体エレクトロニクスの技術革新が原動力である.そしてこのトレンドはPC,スマートフォン,そしてIoT(Internet of Things)へと続く.

最新の半導体技術を活用してコンピュータの小形化,高性能化,低コスト化を実現するという方向はその後,最新の半導体技術で1チップ化可能なコンピュータを開発する方向に移っていった.コンピュータ心臓部の1チップ化,マイクロプロセッサの開発である.

この流れを示す資料として「MICROPROCESSOR EVOLUTION」というMicroprocessor Report誌によるポスターがある(図2).手元にあるものは1996年版でマイクロプロセッサが初めて世に出た1971年から25年間の年表となっている.

プロセッサを1チップ化する目的は,メモリから命令とデータを読み込み,実行するという最も高速化が必要な部分を1チップに集積すること.これによりプロセッサ動作周波数の高速化,低電力化,そして低コスト化が可能になる.しかし,半導体の微細化が不十分な段階ではまだコンピュータのプロセッサ全てを1チップに入れることができなかった.

世界初のマイクロプロセッサは1971年に発表されたIntelの4004で,電卓用の計算回路を4ビットプロセッサとして1チップ化したものである.当時の大形コンピュータは32ビットで,性能でも機能でも大きな開きがあった.その後,ZilogのZ80やMOS Technologyの6502といった8ビットマイクロプロセッサを使ったマイクロコンピュータが登場し,初めはホビー用だったが事務処理用にも使われるようになった.このような状況を踏まえ1981年にIBMが発表したのがIBM PCで,Intelの8088を搭載した.1982年にはAppleがMotorolaの68000を搭載したLisaを発表した.このコンピュータはGUIを備え,Macのベースとなった.8088と68000はいずれも16ビットのマイクロプロセッサで,当時の最先端の半導体技術では16ビットのプロセッサの1チップ化するのがせいぜいであったとも言える.

この状況を変えたのがRISC(Reduced Instruction Set Computer)アーキテクチャである.1970年代後半のIBMの801ミニコンピュータ(2)に端を発するRISCアーキテクチャは,1980年代に入ってBerkeley RISC Iに基づくSUNのSparc,Stanford MIPSに基づくMIPSのR2000としてマイクロプロセッサ化されている.RISCは固定長でシンプルな命令を持ち,レジスタが多く,命令のパイプライン処理を乱さない命令仕様といった命令セットの特徴が注目されやすいが,本質は当時の最新の半導体技術で1チップ化できる32ビットコンピュータの新アーキテクチャの提案であった.つまり,ダウンサイジングを加速するために,実現手段としての半導体技術を優先してアーキテクチャを設計し直したのである.

1990年代に入って動作周波数100MHz超えを果たしたRISCとIntel x86は最新半導体技術で動作周波数の向上を競い,その競争は現在の2~4GHz動作まで続く.

先のポスターには日本のマイクロプロセッサも掲載されている.1980年代後半の富士通,東芝によるTRON,1990年代の日立SH,NEC V810で,いずれもオリジナルアーキテクチャであり,現在の組込みマイクロコントローラの系列につながる.

周波数向上により,プロセッサに読み込まれた命令やデータは高速に実行される.そのため,プロセッサを休まず動作させ続けるには,命令やデータをプロセッサにより高速に転送しなければならない.

一つの解決策はプロセッサ内蔵メモリの高速化と大容量化である.特に命令やデータを供給するキャッシュメモリというSRAM(Static Random Access Memory)は,プロセッサの周波数向上と並行して高速化,大容量化され,それが現在も継続している.

ただ,内蔵できるキャッシュメモリの容量にも限りがある.マイクロプロセッサの外に置かれた外部メモリからの命令やデータの取り込みも高速化しなければならない.つまり,もう一つの解決策はマイクロプロセッサと外部メモリの間のデータ転送の高速化,大容量化である.

コンピュータの主メモリの歴史を振り返ってみる.1960から1970年代に掛けて主メモリには磁気ドラムメモリや磁気コアメモリといった磁気デバイスが使われていたが,DRAMやSRAMといった半導体メモリの登場とともに1980年代以降,これに置き換えられていく.

1980年代,マイクロプロセッサの近くから,高速にデータを供給するキャッシュメモリのSRAM,SRAMほど高速ではないが大量にデータを格納して供給する主メモリのDRAM,そして二次記憶装置の磁気ディスクというようにメモリはきれいに階層化されていた.この時期,キャッシュメモリのSRAMも別チップだったが半導体の微細加工の技術の進展によりSRAM独特の製造プロセスではなくプロセッサと同じロジックプロセスで作れる6トランジスタSRAMがマイクロプロセッサに内蔵されるようになった.現在ではL1,L2,L3(Level 1,2,3)までの階層のキャッシュメモリを内蔵するマイクロプロセッサもある.

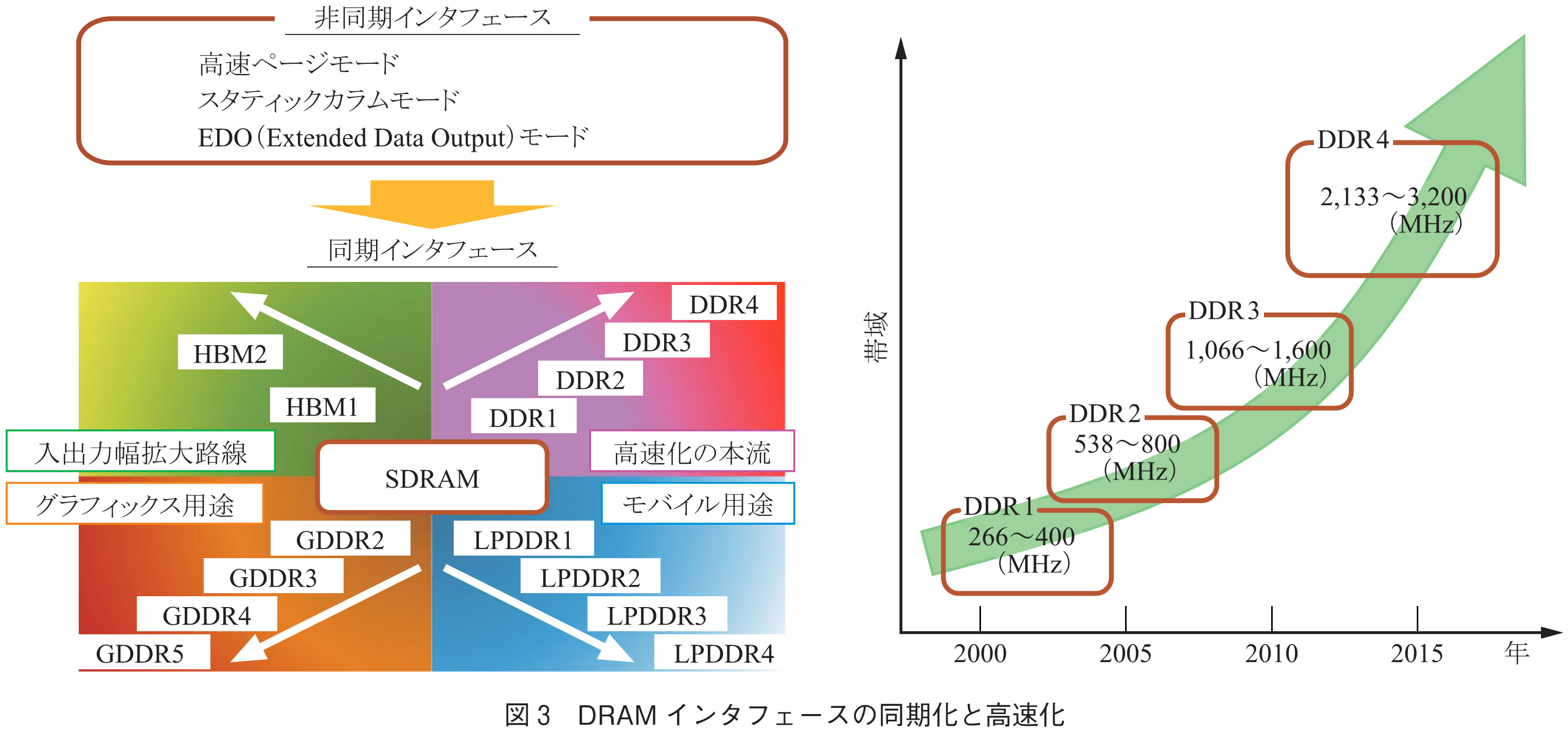

コンピュータのメモリ階層の中間に位置するDRAMは,半導体の微細加工技術の進歩により大容量化したが,同時にDRAMの読み書きインタフェースの高速化が始まった.それまで非同期だったインタフェースが1990年代にプロセッサと同期を取りやすいシンクロナスインタフェースに変わり,その後は周波数を上げることでデータ転送能力を拡大していった.今では,DDR4(Double Data Rate)が既にあり,次の世代は3GHz以上の周波数に対応可能な開発が進んでいる.高速データ転送が要求されるグラフィックス用途で開発されたGDDR5(Graphic Double Data Rate)では既に6GHzの製品が市販され,10GHzを超える製品開発も発表されている(図3).

また,三次元チップ積層技術によりメモリ容量を増やしつつメモリとプロセッサを同じパッケージに実装する新しいメモリモジュールが提案されている.その一つはHMC(Hybrid Memory Cube)(3)というDRAMモジュールで,プロセッサ直近に配置することで高周波数のパケットプロトコルによる高速インタフェースを実現する.もう一つがHBM(High Bandwidth Memory)(4)というDRAMモジュールで,インタフェースを高周波数化する代わりに周波数は1GHz程度にとどめ,入出力ピン数を1,024本と大幅に拡大することでデータ転送の高速化を実現する.HMCとHBMはDRAMをTSV(Through Silicon Via)という結線技術で積層して小さな面積で大容量のメモリモジュールを実現する.DRAMの大容量化と同様,高速化もまた半導体の回路技術,微細化技術の革新により実現されてきた.

コンピュータの二次記憶装置としてプロセッサから一番遠い位置にある磁気ディスクは,ハードディスクと名を変えて今もその位置を確保しているが,フラッシュメモリの登場で立場を弱めているのが現状である.フラッシュメモリは動作速度が遅く,信頼性耐性に課題が残るが,高集積化により安価で大容量なメモリデバイスとして有効性を発揮している.更に,多数のフラッシュメモリで構成されたSSD(Solid State Drive)というメモリデバイスがハードディスクの用途を置き換え始めている.フラッシュメモリ自身は平面的な微細加工による高集積化が限界にきており,現在はこれを積層する三次元での高集積化の競争が激しくなっている.

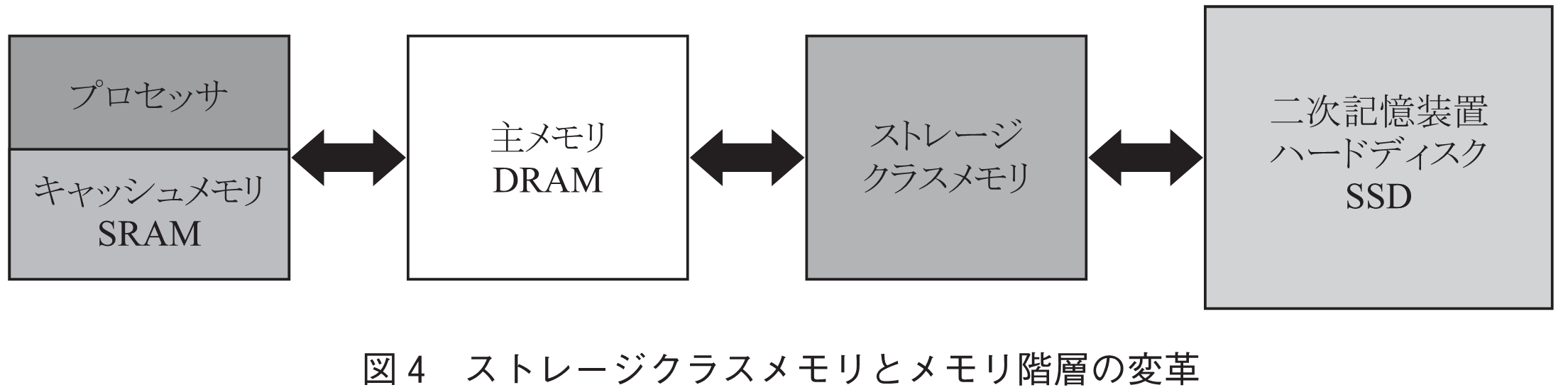

コンピュータのメモリ階層として長い間続いてきたキャッシュメモリ(SRAM),主メモリ(DRAM),二次記憶装置(ハードディスクやSSD)に,現在,最新のエレクトロニクス技術を反映して変革の兆しが出てきた.主メモリのDRAMと二次記憶のハードディスク,SSDを比べるとデータ転送速度が大幅に異なり,大きな性能ギャップがある.そのギャップを埋めるメモリとしてストレージクラスメモリと呼ばれる新たなメモリ階層が検討されている(図4).この階層のメモリデバイスとして電子スピンや結晶構造の変化を利用したメモリ,絶縁膜内にフィラメントを形成するメモリ,サイリスタ,カーボンナノチューブを利用するメモリなど様々なメモリデバイスが提案されている.コンピュータのメモリ階層もまた最新のエレクトロニクスの進歩を受けて変革の可能性が訪れている.

半導体の高速化,高集積化によりマイクロプロセッサを高周波数化し,内蔵メモリを高速・大容量化した上で更に高性能なコンピュータを実現するには,プログラム実行を並列化する以外に手はない.2000年代に入ってから,微細化によって一つのプロセッサをより大容量のキャッシュメモリとともに1チップに集積するという選択肢以外に,複数のプロセッサを1チップに内蔵するという新たな選択肢が見えてくるようになった.マルチコアの1チップ化である.

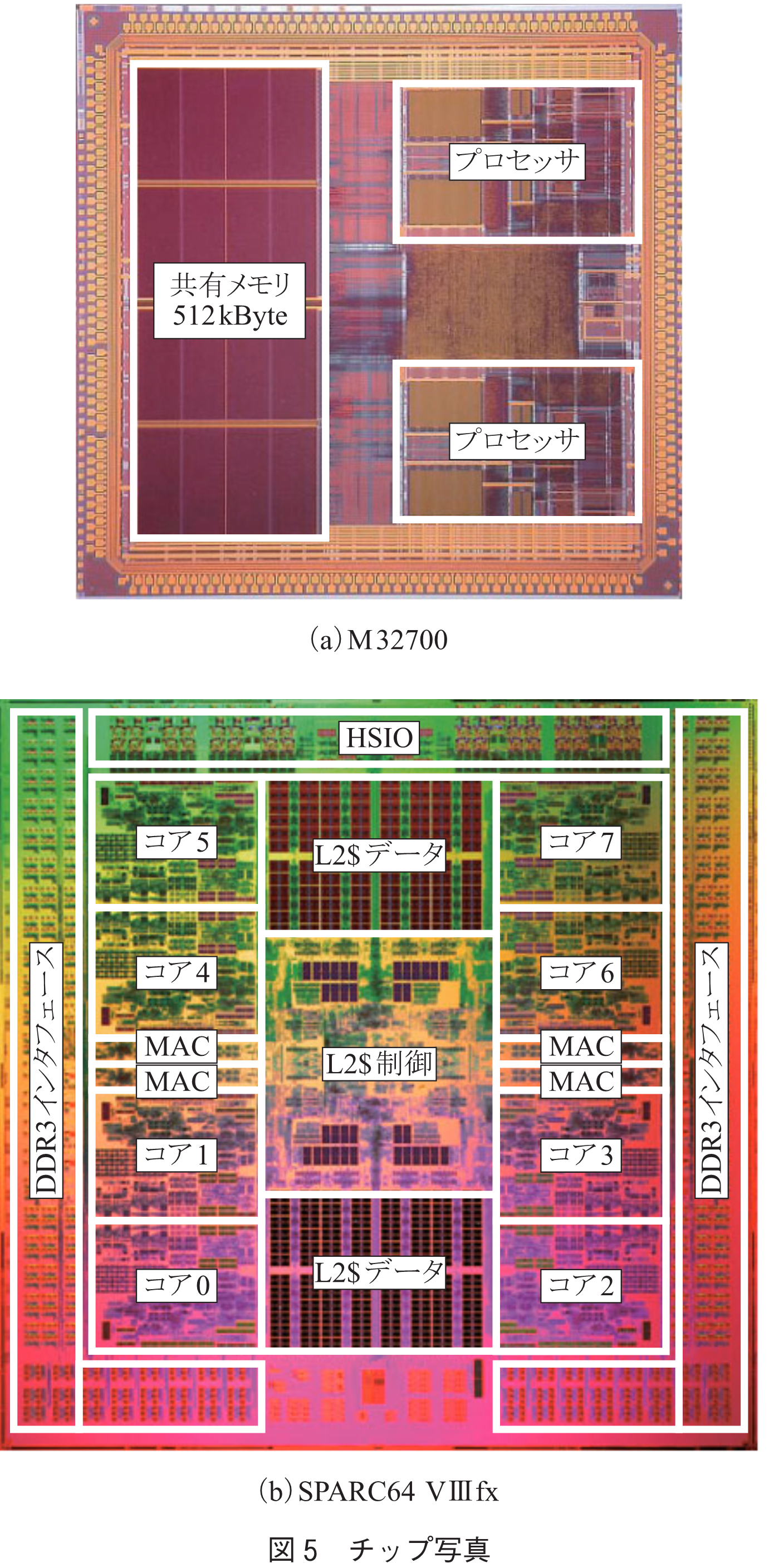

ここに2003年のISSCCで発表された三菱電機M32700(5)を一例として示す(図5).マルチコアマイクロプロセッサの先頭を切ったチップの一つである.600MHzで動作する二つのプロセッサコアが128ビットの内部バスを通じて512kByteの主メモリを共有したSMP(Symmetric Multiprocessing)システムが1チップに内蔵されており,LinuxのSMP OSによるプログラムの並列処理が実現されている.このようなマイクロプロセッサがタイムリーに開発された背景には,150nmという微細化製造プロセスが使えたことに加えて,Linux SMP OSがオープン化されていたというソフトウェア面,そして大容量のFPGAチップを使ったハードウェア・ソフトウェアのコ・デザイン(マルチコアとLinux SMPのコ・デザイン)が可能になったという設計技術面での進展があった.このような技術環境の変化により,これ以降,マルチコアマイクロプロセッサの開発が主流となっていく.例えば,M32700のマルチコア技術はルネサスエレクトロニクスのマイクロコントローラSHのマルチコア化に展開されていった.

より高性能なレンジを狙った日本のマルチコアマイクロプロセッサの例として2009年のHot Chipsで発表された富士通のSPARC64 VIIIfx(6)を示す(図5).このチップは45nmの製造プロセスによって2GHz動作の八つのコアと6MByteのL2キャッシュを内蔵したマルチコアマイクロプロセッサで,スーパコンピュータ「京」に88,128個搭載され,それらはTofuインターコネクトと呼ばれる六次元メッシュ/トーラスで結合されて超並列処理スーパコンピュータを構成している.「京」は2011年の稼動開始時に,Linpackベンチマークでの性能ランキングで世界1位となった(7).

現時点での日本最高性能のスーパコンピュータは2016年に稼動した東大・筑波大のOakforest-PACS(8)で,そのピーク性能は25PFLOPSである.このシステムは,一つのチップに64個のコアを搭載するメニーコアプロセッサ(Intel Xeon Phi 7250,1.4GHz)を採用する.このように,1チップに搭載されるコア数は引き続き増大している.各プロセッサは,高バンド幅メモリとして16GByteのMCDRAM(Multi-chip DRAM)と,従来と同等バンド幅のメモリとして96GByteのDDR4メモリを搭載する.MCDRAMは3.2で述べたHMC技術が実装されたものである.Oakforest-PACSではこのプロセッサが8,208個,100Gbit/sのフルバイセクションバンド幅Fat-Treeネットワークで結合されている.一般にトポロジーがトリー構造である場合には根(Root)に近い部分に通信が集中し性能のボトルネックとなるが,このネットワークでは,根に近い部分の通信路を太く(Fatに)することで,任意の二つのコア間で100Gbit/sのバンド幅が実現されている.またストレージに関しては,総容量26.2PByte,総バンド幅500GByte/sの並列ファイルシステムを備えるとともに,高速なストレージとしてSSDで構成される総容量940TByte,総バンド幅1.56TByte/sの高速ファイルキャッシュシステムをも有することで,二次記憶へのアクセスを強化している.

スーパコンピュータの性能はこれまでほぼ4年で10倍の性能向上を果たしてきており(9),今後もこのペースで向上すると予測されている.チップだけでなく,メモリ技術,パッケージング技術,チップを多数結合するネットワーク構成とそれを実装したボード,そのボードを多数結合して構築する技術,更にはストレージ技術の全てがエレクトロニクス技術の集積と考えられるだろう.

コンピュータシステムの高性能化の歩みについて,プロセッサの高周波数化,メモリとのデータ転送の拡大,プログラムの並列実行の三つの軸で高性能化に対する半導体技術やエレクトロニクスの寄与を振り返った.現在,高性能化の最大の課題は高周波数化と大規模並列処理による消費電力,発熱の増大であり,エレクトロニクス面で新たな素子や動作原理が期待されている.また超大規模な並列処理の実現が視野に入り,機械学習やAIの分野との技術交流の重要性も増してきた.コンピュータシステムはこれからもエレクトロニクスの進歩と表裏一体で進化し続けるであろう.

(1) トレイシー・キダー,超マシン誕生,糸川 博(訳),日経BP社,2010.

(2) J. Cocke and V. Markstein, “The evolution of RISC technology at IBM,” IBM J. Res. Dev., vol.34, no.1, pp.4-11, April 1990.

(3) Hybrid Memory Cube Consortium,

http://www.hybridmemorycube.org/

(4) D.U. Lee, K.W. Kim, K.W. Kim, H. Kim, J.Y. Kim, Y.J. Park, J.H. Kim, D.S. Kim, H.B. Park, J.W. Shin, J.H. Cho, K.H. Kwon, M.J. Kim, J. Lee, K.W. Park, B. Chung, and S. Hong, “A 1.2V 8Gb 8-channel 128GB/s high-bandwidth memory (HBM) stacked DRAM with effective microbump I/O test methods using 29nm process and TSV,” 2014ISSCC, no.25.2, pp.432-433, Feb. 2014.

(5) S. Kaneko, K. Sawai, N. Masui, K. Ishimi, T. Itou, M. Satou, H. Kondo, N. Okumura, Y. Takata, H. Takata, M. Sakugawa, T. Higuchi, S. Ohtani, K. Sakamoto, N. Ishikawa, M. Nakajima, S. Iwata, K. Hayase, S. Nakano, S. Nakazawa, O. Tomisawa, and T. Shimizu, “A 600MHz single-chip multiprocessor with 4.8GB/s internal shared pipelined bus and 512kB internal memory,” 2003ISSCC, no.14.5, pp.254-255, Feb. 2003.

(6) T. Maruyama, T. Yoshida, R. Kan, I. Yamazaki, S. Yamamura, N. Takahashi, M. Hondou, and H. Okano, “Sparc64 VIIIfx: A new-generation octocore processor for petascale computing,” IEEE Micro, vol.30, no.2, pp.30-40, April 2010.

(7) TOP500 The List,

http://www.top500.org

(8) Basic Specification of Oakforest-PACS,

http://jcahpc.jp/files/OFP-basic.pdf

(9) 小柳義夫,中村 宏,佐藤三久,松岡 聡,岩波講座 計算科学 別巻 スーパーコンピュータ,岩波書店,2013.

(平成29年3月31日受付 平成29年4月19日最終受付)

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード