|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

電子スピンの回路とシステムへの応用

小特集 5.

バッファメモリ向け三次元積層CIS対応40nm混載STT-MRAMの開発

3D Stacked CIS Compatible 40nm Embedded STT MRAM for Buffer Memory

Abstract

スピン注入書込み型MRAM(STT-MRAM)の研究開発が精力的に進められており,なかでもロジック混載STT-MRAMは今後市場の拡大が期待されている.我々は積層CISプロセスに適合する40nmロジック混載STT-MRAM開発を行い,動作を実証した.MTJ材料及びプロセスの改善により,積層プロセスに耐え,かつバッファメモリ向けの高速書込みと高エンデュランスを実現したことが特徴である.本稿ではロジック混載STT-MRAMの一般的な特長や開発動向を概観し,我々の成果を紹介する.

キーワード:STT-MRAM,三次元積層CIS,バッファメモリ,不揮発メモリ

スピン注入書込み型MRAM(STT-MRAM)は,記憶素子であるMTJ(Magnetic Tunnel Junction)を構成する磁性膜の磁化配置によって抵抗値が変化する抵抗変化型メモリである.書込みにはスピントランスファトルクを利用しているため,従来の電流磁界書込み型MRAMに比較して消費電力を著しく低減できることから,その性能と製品応用に注目が集まり,各社で精力的な研究開発が進められてきた(1)~(7).

ソニーセミコンダクタソリューションズ株式会社において,積層CIS(CMOS Image Sensor)プロセスに適合する40nmロジック混載STT-MRAM開発を行い,動作を実証した(8).本稿では,まずSTT-MRAMの動作原理と特徴,課題について概観し,続いて我々の開発成果について説明する.

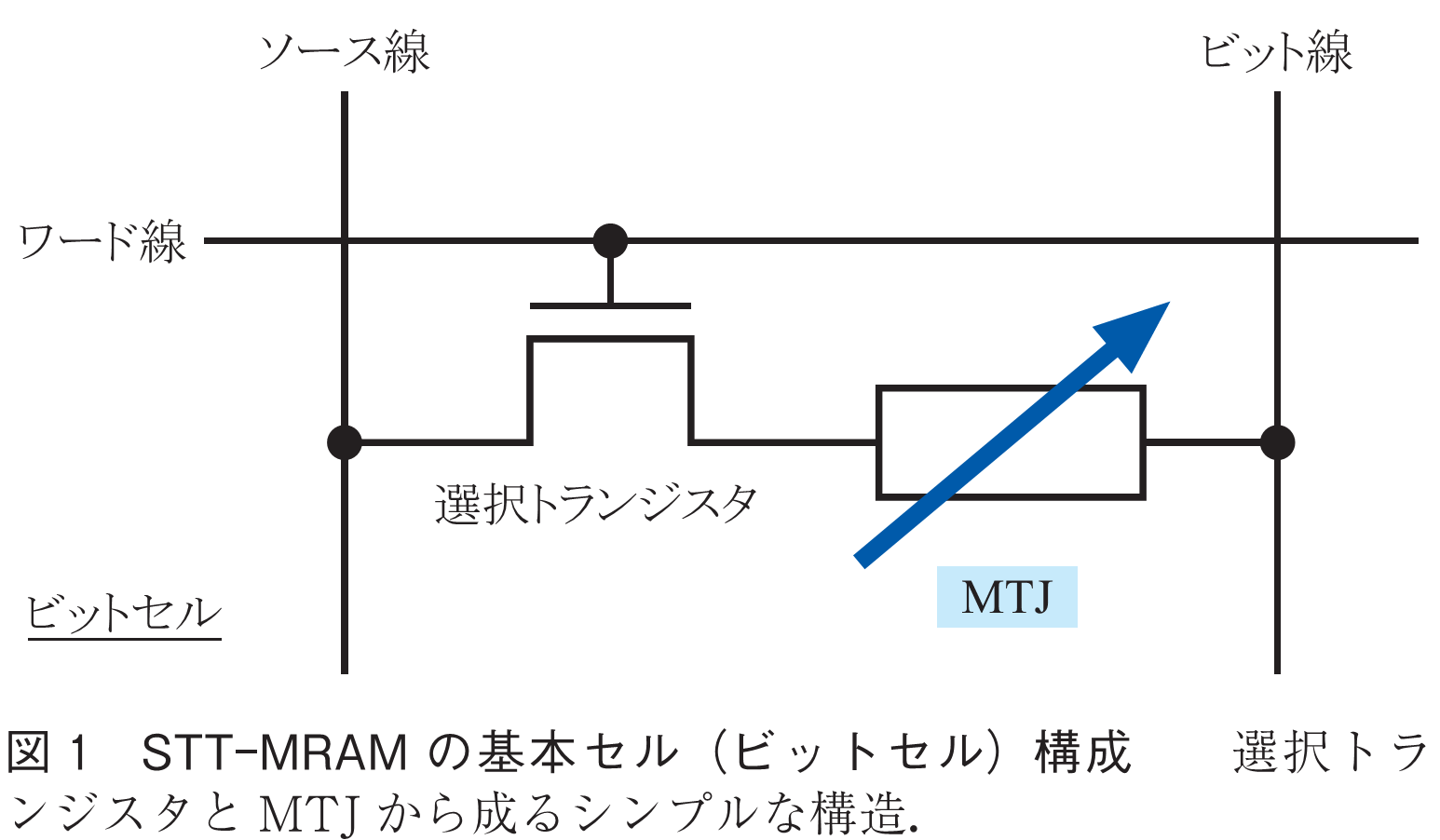

STT-MRAMの基本セル構造を図1に示す.選択トランジスタと記憶素子MTJから成るシンプルな構造である.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード