|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

3.半導体技術を利用したイジングマシンの実現と応用

小特集 3-1

CMOSアニーリングマシンの概要と開発状況

Outline and Development Status of CMOS Annealing Machine

abstract

IoTが一般的となり必要な計算能力は増大しているが,従来の計算機の性能向上は半導体微細化の鈍化とともに困難となっている.そこで,処理対象を組合せ最適化問題に特化し,最適化問題をイジングモデルに写像し効率良く解くアニーリングマシンが提案されている.ここでは,半導体回路でイジングモデルを擬似的に再現するCMOSアニーリングマシンを紹介する.このCMOSアニーリングマシンのプロトタイプを開発し,組合せ最適化問題が処理できることを確認した.更に実用化に向けてアプリケーションやソフトウェア技術の開発を行っており,その詳細を解説する.

キーワード:組合せ最適化,CMOSアニーリングマシン,イジングモデル,新概念計算機

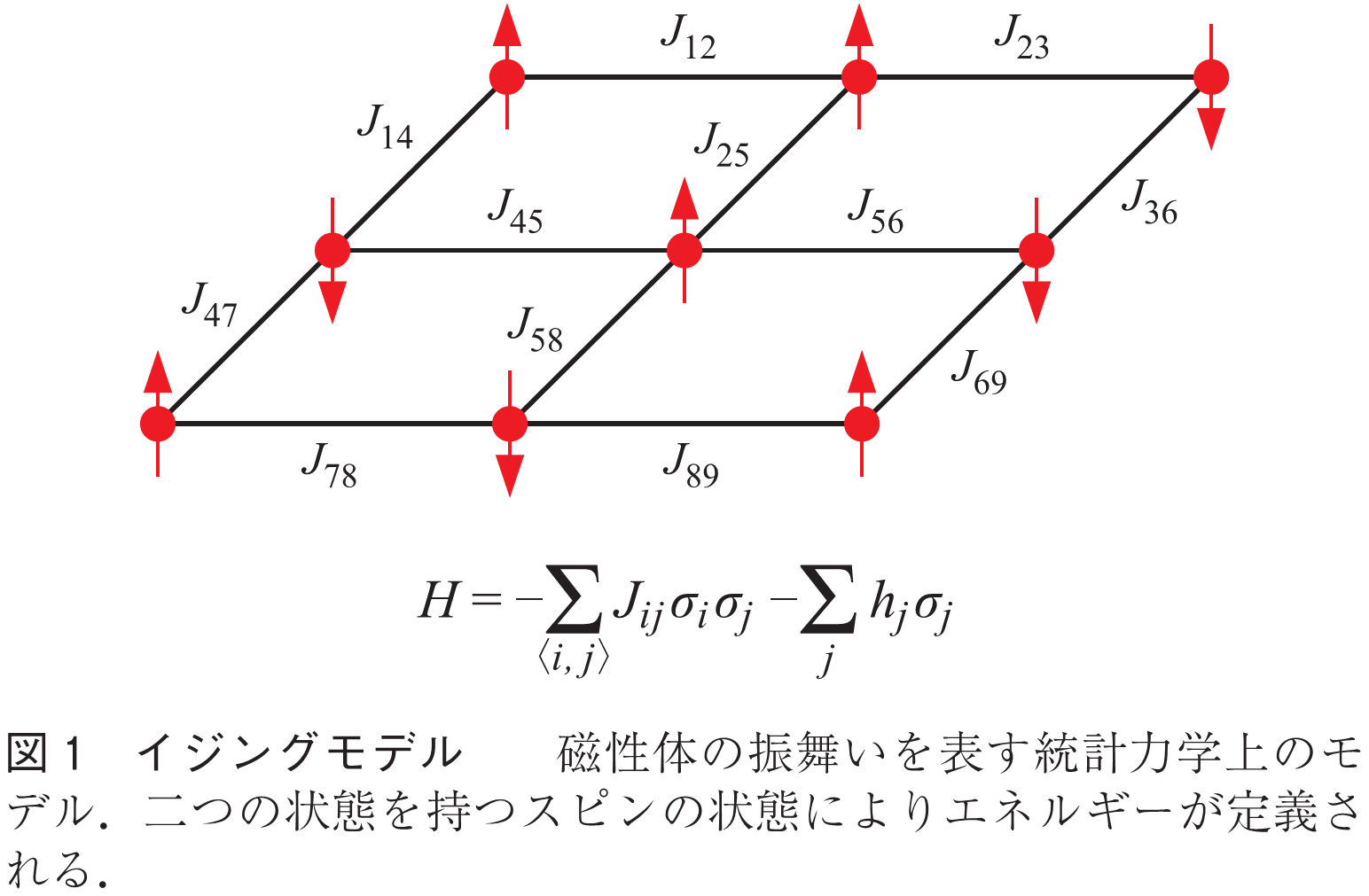

IoT(Internet of Things)が一般的となり,実社会にある様々なセンサにおいて多くのデータが収集され,それに伴い,そのデータ処理を行うために必要となる計算量は増大している.一方で,半導体の微細化は終えんが近いと言われており,従来のノイマン形計算機の性能向上は頭打ちとなっている.また,従来は収集されたデータは単に数値計算を行って使われるデータとして加工されていたが,今後は,必要なパラメータの最適な組合せを探す等の最適化処理など,これまでと異なる用途にも使われ始めている.そこで,こういった特定の処理に絞って高速に計算する新しいコンピュータが提案されている(1),(2).その一つとして,組合せ最適化問題を効率良く処理するために,磁性体の振舞いを表す統計力学上のモデルであるイジングモデルを用いるアニーリングマシンと呼ばれるコンピューティング技術が提案されている.その一つの実装として,半導体回路を用いてイジングモデル(図1)を模擬するCMOSアニーリングマシンを提案した(3)~(5).このCMOSアニーリングマシンのプロトタイプを試作し,実際に組合せ最適化問題が解けることを確認するとともに,様々な実装により,より複雑な組合せ最適化問題が解けることを確認した.本稿では,このCMOSアニーリングマシンが,IoTのエッジ及びクラウドの両方で使える技術であることを説明するとともに実用化に向けて必要な技術を紹介する.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード