|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

シリコンフォトニクスを用いた光通信素子の研究開発最新動向

5.

フルメッシュ波長ルーチングで接続されたFPGAを搭載した省エネルギー高性能サーバシステム

An Energy-saving High-performance Server System with FPGAs Fully Connected by Wavelength Routing

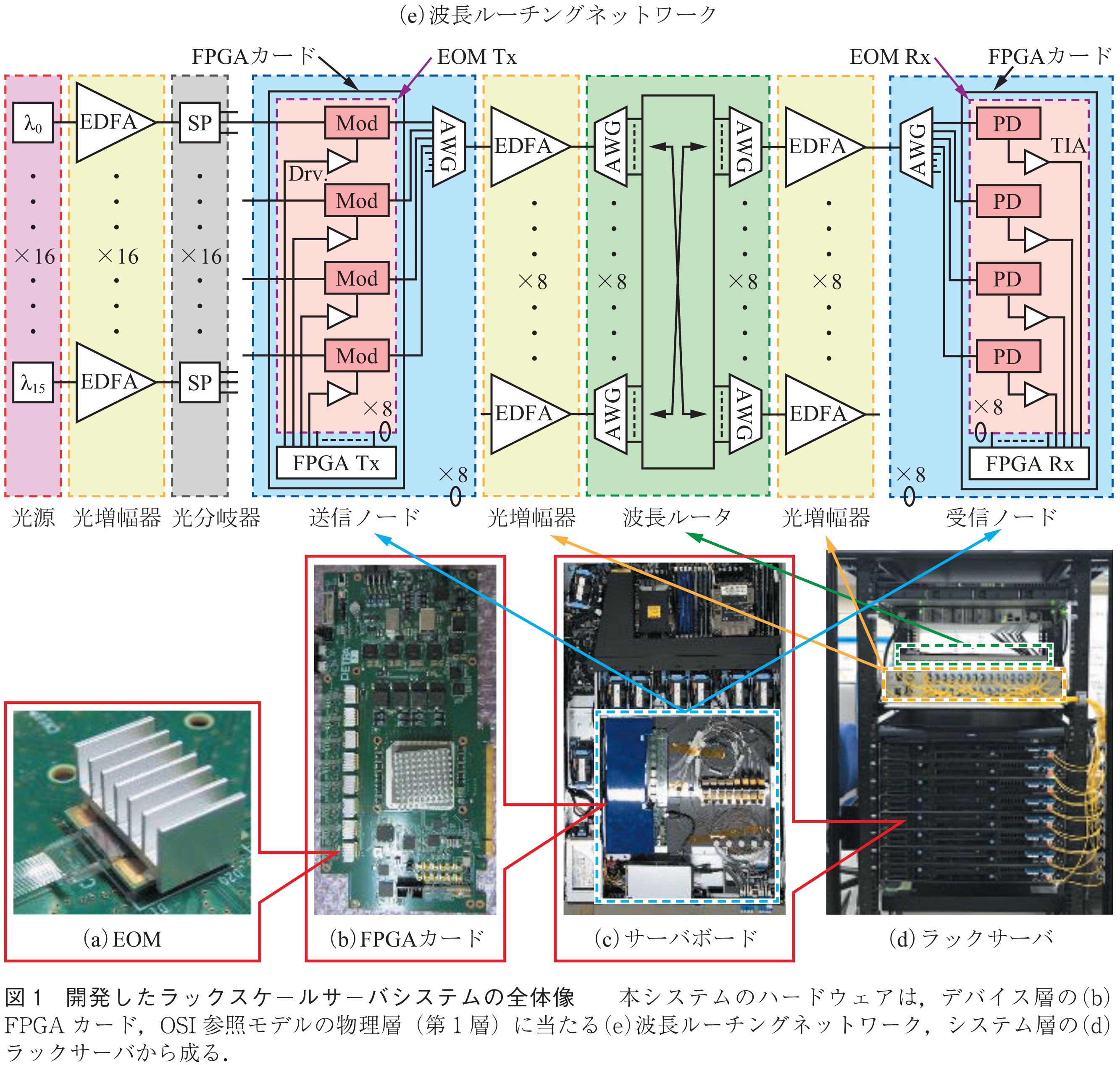

シリコンフォトニクスを用いたDWDM対応高帯域密度光送受信モジュール,800Gbit/sのメモリ及びネットワーク帯域幅を持つFPGAカード,波長ルーチングを用いた省エネルギーFPGA間フルメッシュネットワーク,これらのハードウェアに最適化したデータリンク層アーキテクチャOPTWEB及び並列ソーティングアルゴリズムなど,デバイスからアプリケーションまでの協調設計により,省エネルギー高性能サーバシステムを開発し,電気配線サーバと比較して48倍の高速化と98%のエネルギー消費量削減を実証した.

キーワード:シリコンフォトニクス,FPGA,波長ルーチング,サーバ,ソーティング

近年,処理すべきデータ量は指数関数的に増大する一方で,単体CPU(Central Processing Unit)の演算性能の伸びは鈍化している.そのギャップを埋める手段として,多数の計算ノードによる並列分散処理及びアクセラレータを用いたヘテロジニアス計算が普及している.このようなシステムでは,アクセラレータ間の通信性能がシステム全体の性能のボトルネックとなり得る.また,データセンタにおける消費エネルギーの増大も懸念されている.

そこで我々は,これらの課題を解決するため,各計算ノードにアクセラレータとしてFPGA(Field Programmable Gate Array)が搭載され,FPGA間が波長ルーチングで光接続された省エネルギー高性能なラックスケールサーバシステムを開発した.本サーバシステムの全体像を図1に示す.本システムのハードウェアは,デバイス層の(b)FPGAカード,OSI参照モデルの物理層(第1層)に当たる(e)波長ルーチングネットワーク,システム層の(d)ラックサーバから成る.更に図1には記載していないが,OSI参照モデルのデータリンク層(第2層)としてOPTWEB,及びアプリケーション層として並列分散ソータと合わせて,五つの技術層から成る.次章以降で,各技術層について述べる.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード