|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

CMOSインバーティブルロジック[Ⅱ]

――設計手法とツール――

CMOS Invertible Logic[Ⅱ]: Design Method and Tools

第1回で,双方向計算を既存のハードウェア上で実装可能なCMOSインバーティブルロジックの概要について説明を行った.典型例であるインバーティブルAND(IL-AND)ゲートを対象に,双方向計算を行う関数を表現するためのハミルトニアン係数と雑音制御による双方向計算の様子を紹介した.今回は,任意の関数に対するハミルトニアンの生成手法,及び自動設計ツールについて解説を行う.

ANDなどの論理ゲートのような小規模関数は,線形計画法により対応するハミルトニアン係数を決定することが可能である(1).ハミルトニアン(エネルギー)は前回も説明したとおり,

(1)

で定義される.ここでいうハミルトニアン係数とは,

であり,

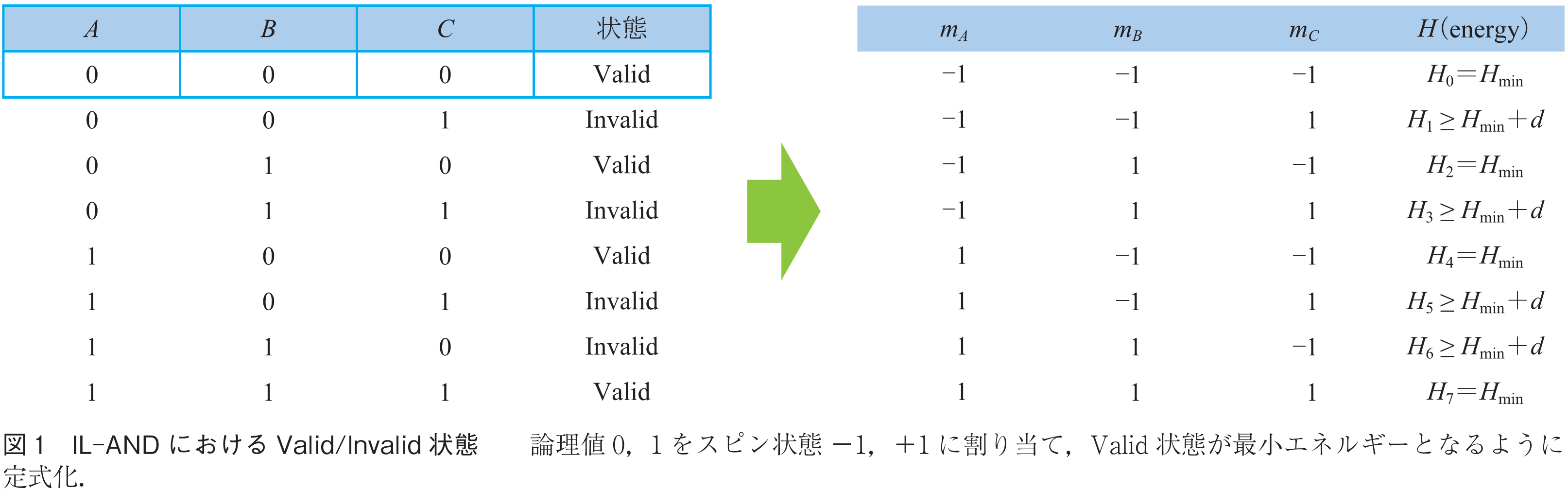

はスピンの状態(-1 or +1)を表す.図1にIL-AND(

)のハミルトニアン係数の生成手順を示す.全部で8状態存在し,ANDの真理値表を満たす

,

,

の状態はValid,それ以外の状態はInvalidと定義される.

IL-ANDのハミルトニアン係数の生成方法について説明をする.まず,スピンの状態は-1と+1を取るため,論理値‘0’をスピン状態

,論理値‘1’を

に変換する.次に,それぞれの状態におけるハミルトニアンを式(1)に基づいて定義する.インバーティブルロジックでは,Valid状態におけるハミルトニアンが最小(

)となり,Invalid状態におけるハミルトニアンがそれより大きい必要がある.そのため,任意の関数

(

は入力,

は出力を表し,それぞれ実数)に対して,Valid及びInvalid状態におけるハミルトニアン(

)は以下のように定義される.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード