|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

AIチップに向けた不揮発性メモリ技術とその展望

小特集 2.

三次元フラッシュメモリ技術とニューラルネットワーク応用

3D Flash Memory Technologies and Its Application for Artificial Neural Networks

Abstract

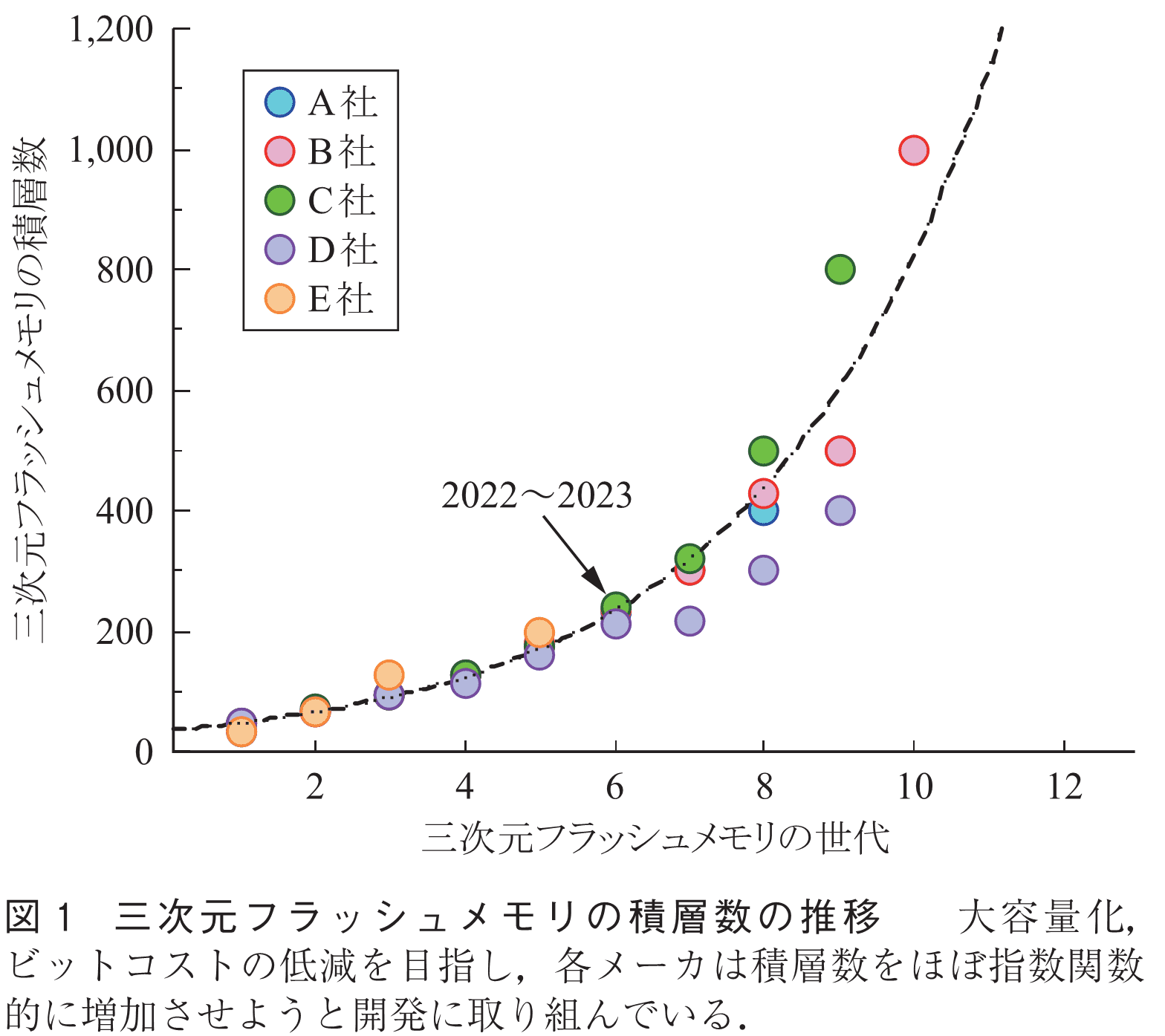

超情報化社会の「データ記録」を担っている三次元フラッシュメモリは,300層を超える高層化も開発されるなど縦に高積層化することで更なる大容量化が進められている.しかし,積層数を増やし続けるためには多くの課題があり,それを解決する新技術が必要不可欠である.更に,三次元フラッシュメモリの特異なアーキテクチャと大容量であることを利用したニューロモルフィックコンピューティング応用など,単なる“記録媒体”だけではない新たな展開も注目されている.本稿では,このような大容量三次元フラッシュメモリのセル技術とそれを用いたニューラルネットワーク応用の動向を述べる.

キーワード:三次元フラッシュメモリ,メモリセル,高積層化技術,ニューラルネットワーク

1980年代に開発された電気的書換え可能な半導体不揮発性メモリであるフラッシュメモリ(1)は,昨今の超情報化社会が生み出す膨大な情報を扱う記録媒体としてより大容量化が求められている.その要求を満たす革新的な技術として,近年メモリセルを縦に積層した三次元フラッシュメモリ技術が開発されスマートフォンやパソコン市場にも普及している(2),(3).三次元フラッシュメモリの構造はシリコン基板上にメモリセルが並んだ従来の平面構造NANDフラッシュメモリと異なり,縦方向にメモリセルを積み上げた形となる(4)~(9).したがって,素子を微細に製造し単位面積当りのメモリセル数を増加させるという従来のアプローチではなく,縦方向の積層数を増大させることで大容量化を実現する.図1に示すとおり,2023年度の開発レベルでは300層を超えており,今後500層以上という構想も議論に上がってきている(10).

本稿では,このような大容量メモリに向けた高積層化を実現するにあたり顕在化する課題とその解決に向けた技術的な取組みを前半で述べる.続く後半では,三次元フラッシュメモリの特異的なアーキテクチャや高密度である特徴を利用してニューラルネットへの応用が近年盛んに検討されているので,その特徴や実施例を紹介したい.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード