|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

AIチップに向けた不揮発性メモリ技術とその展望

小特集 6.

スピントロニクス技術の進展とMRAM,論理演算素子への応用

Recent Advancements of Spintronics Technologies and the Application to Logic-gates

Abstract

MRAMは,スタンドアローン用不揮発性メモリ,並びに混載用不揮発性メモリとして実用化され,スピントロニクス技術の進展に伴い高集積化,書込み・読出しスピードの高速化が進展してきた.具体的には,磁界書込み原理,STT書込み原理,垂直磁化方式のMTJを用いたSTT書込みといった新たな原理の書込み技術の開発が高集積化及び書込みスピードの高速化に寄与し,GMR効果,TMR効果,MgOトンネル障壁を用いたTMR効果増大といった新たな読出し技術の開発がMRAMの高集積化,読出しスピードの高速化に寄与してきた.一方,これらの先の技術として位置付けられて期待されているスピントロニクス技術として「SOT書込み原理」と「VCMA効果を利用した電圧書込み原理」があり,これら新規スピントロニクス技術をいかにMRAMあるいは他のセミコンダクタ製品に応用していけるかが,実用化研究・開発の焦点となっている.本稿では,これら新規スピントロニクス技術に焦点を当て,その実用化研究・開発の現状についてレビューする.

キーワード:スピントロニクス,MRAM,SOT,Logic-gate,Strain

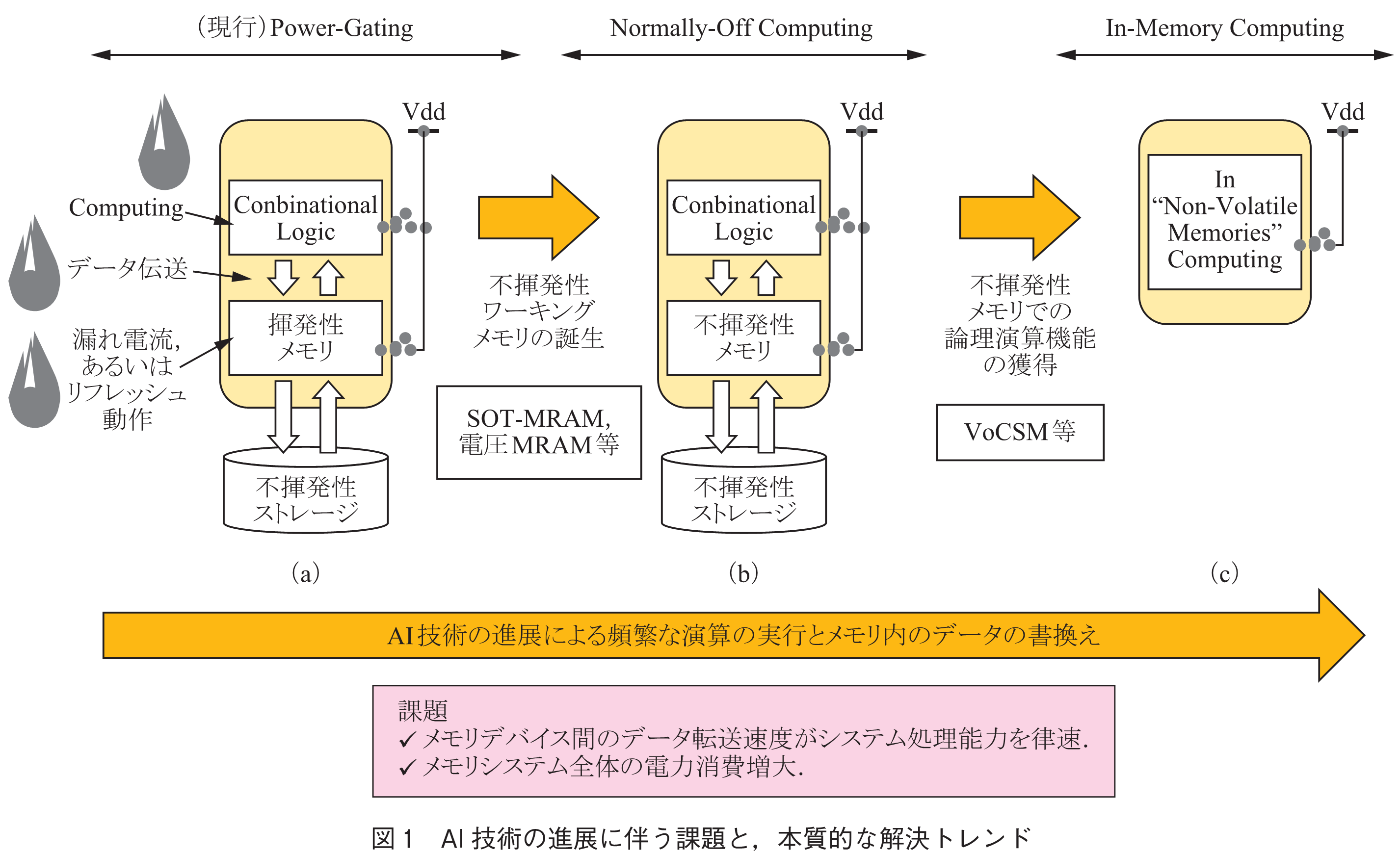

図1(a)に現在使用されている典型的なメモリ階層を示す.Combinational Logicと直接データのやり取りをするメモリには高速な揮発性のCache(SRAM)やDynamic Access Memory(DRAM)が使用されている.これらの下層に不揮発性のNANDフラッシュメモリやHard Disk Drive(HDD)が使われている.

近年Artificial Intelligence(AI)技術が実用化されており,今後一層広く使用されると予想される.AIではこれまでの使い方に比べ桁違いに頻繁な演算の実行とメモリ内のデータの書換えが必要となる.その結果,メモリデバイス間のデータの転送速度がシステムの動作速度を律速し,またメモリシステム全体の消費電力を桁違いに増大させる.

もし,書換え回数制限がなく高速で動作する不揮発性メモリができれば,図1(b)に示すようにメモリ階層を単純化でき,この課題を本質的に解決できる.理想的には,演算機能を併せ持つ不揮発性メモリができれば,同図(c)に示すような究極の形態となり得る.

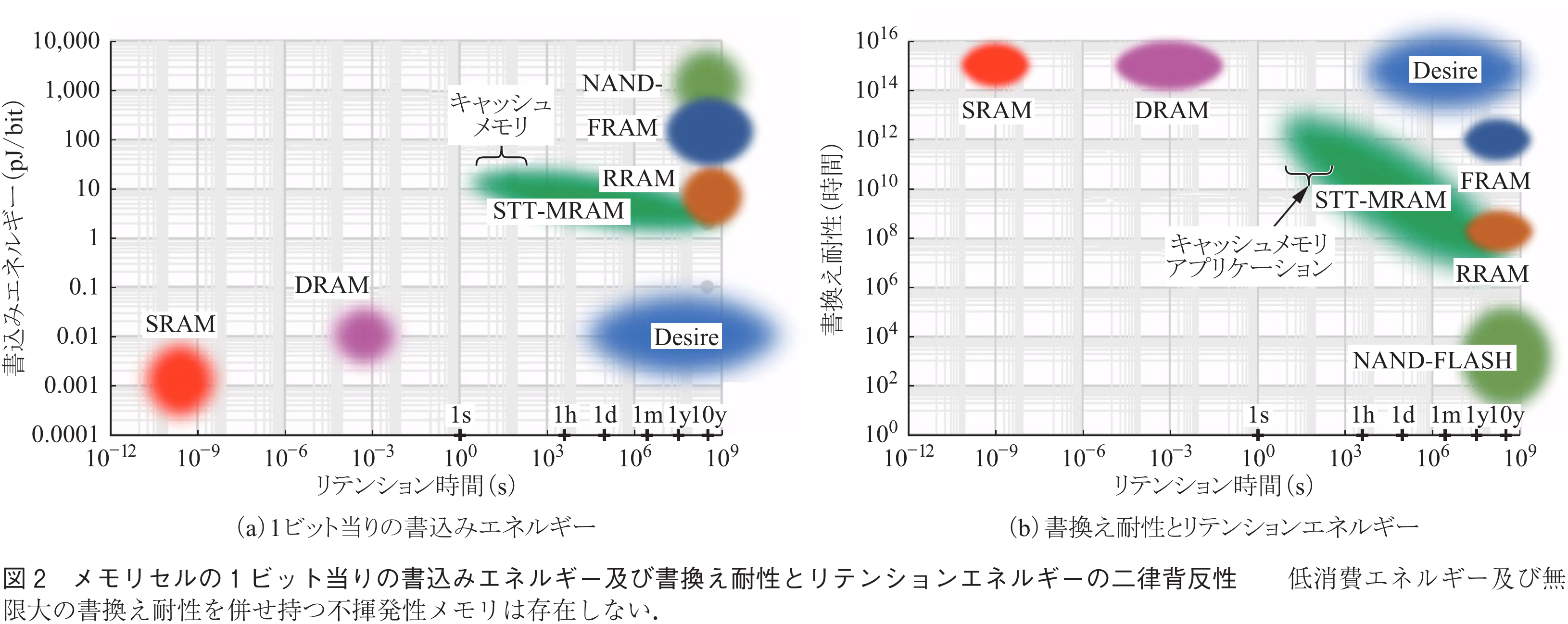

図2に現状のメモリとそれらの1ビット当りの書込みエネルギーとEndurance(書換え耐性)のリテンション時間(記憶保持時間)との相関を示す.同図から読み取れるように,低エネルギー書込み,及び書換え耐性は,不揮発性と二律背反の関係にある.不揮発性メモリの書込みエネルギーは揮発性メモリに比べて,2桁~3桁以上も大きく,書換え耐性も2桁以上悪い.

データを不揮発性にするためには,データ“0”とデータ“1”との間のエネルギー障壁を大きく(概略80kBT程度に)設定する必要があり,これは書込みエネルギーを増大させる.その結果書換え耐性も劣化する.よって,この二律背反性は本質的な問題であり,この二律背反を解くメモリ(同図に“Desire”として示す)が生まれなかったことも納得できる.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード