|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

解説

RISC-Vとオープンハードウェアと日本の半導体業界の未来[Ⅲ・完]

――半導体製造のオープン化,技術蓄積と日本の将来――

RISC-V, Open Hardware and the Future of Japanese Semiconductor Industry[Ⅲ・Finish]: Open Semiconductor Manufacturing, Technology Assets and Future of Japan

A bstract

最終回[Ⅲ・完]ではRISC-Vの勢いの発展を解説する.オープン規格から始まり,実装のオープンソース化,そして半導体製造におけるツールのオープン化の波を生み,論理回路データからRISC-V実チップの製造を個人でお願いできる環境が実現した.米国,EUと日本でファウンドリー工場増設に合致して,RISC-Vは本工場の高稼動率に寄与するとの認識が強まっている.海外が先行するRISC-V技術開発において日本では技術蓄積の過程で欧米との差が見られ,RISC-Vによる持続的技術開発とその蓄積は,ディジタル技術分野での日本の国際的競争力の向上に資する.

キーワード:RISC-V,セキュリティ,AI,オープンソースPDK,ディジタル技術,輸出競争力

RISC-Vの製造についても新しい動きがある.それは「オープンソースPDKムーブメント」と呼ばれる動きである.これが何かというと「半導体(ASIC)製造の民主化」であり,すなわち,誰もが半導体製造ができる世界の到来である.

これまでの半導体製造において,EDA(Electronic Design Automation)ツールは一式そろえれば数億円かかり,ファブごとのPDK(Process Design Kit)はNDA(Non-Disclosure Agreement)がなければ見ることさえできなかった.そのため,半導体製造はそれなりの資金力のある人たち(企業や研究室)に限られており,更にNDAによりその人たちの横のつながりも分断されていた.

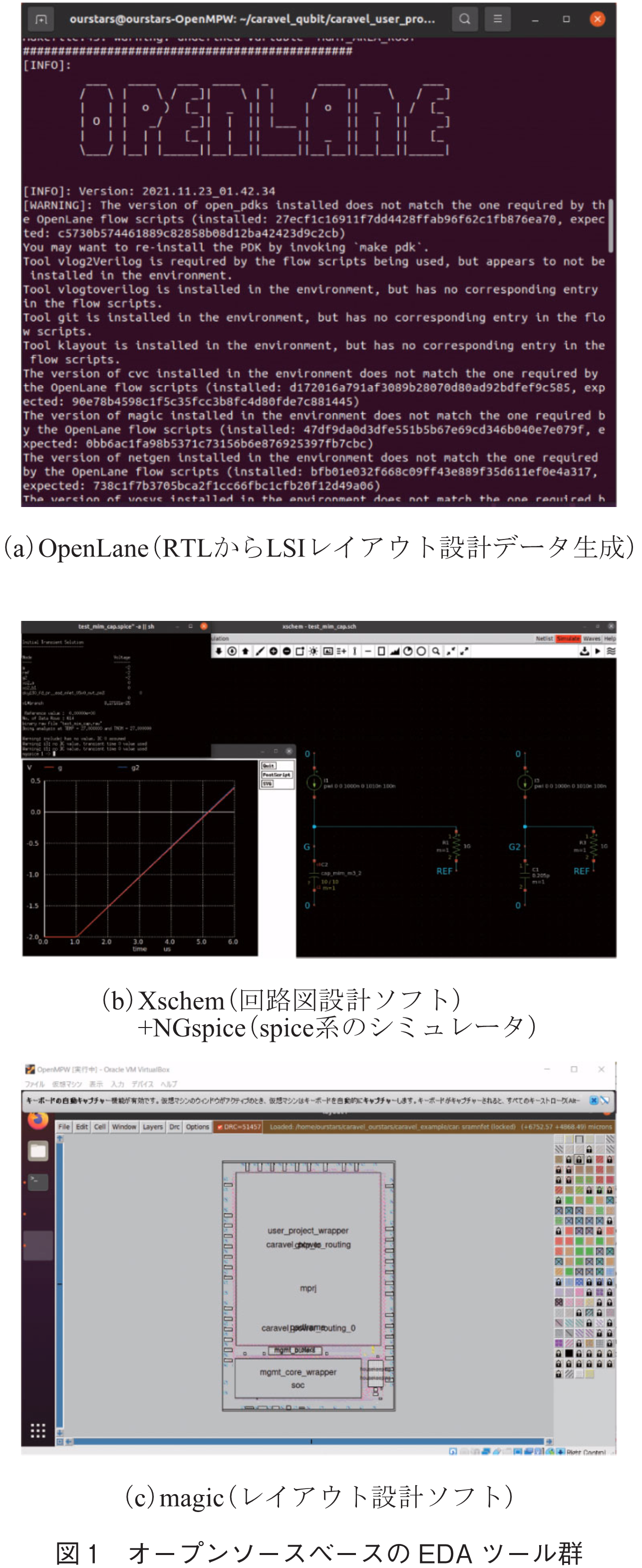

しかし,2006年頃から始まった「第三の産業革命」と呼ばれるメイカームーブメントが起き,オープンソースのEDAツールを用いて半導体製造をする人たちが情報発信をするようになってきた.そして,ついに2020年にEDAツールやPDKが全てオープンソース(図1)で,シャトルでの製造まで無料というサービスが登場し,これまで一部の人たちしかアクセスできず,断絶されていた半導体製造の世界に民主化が始まった.

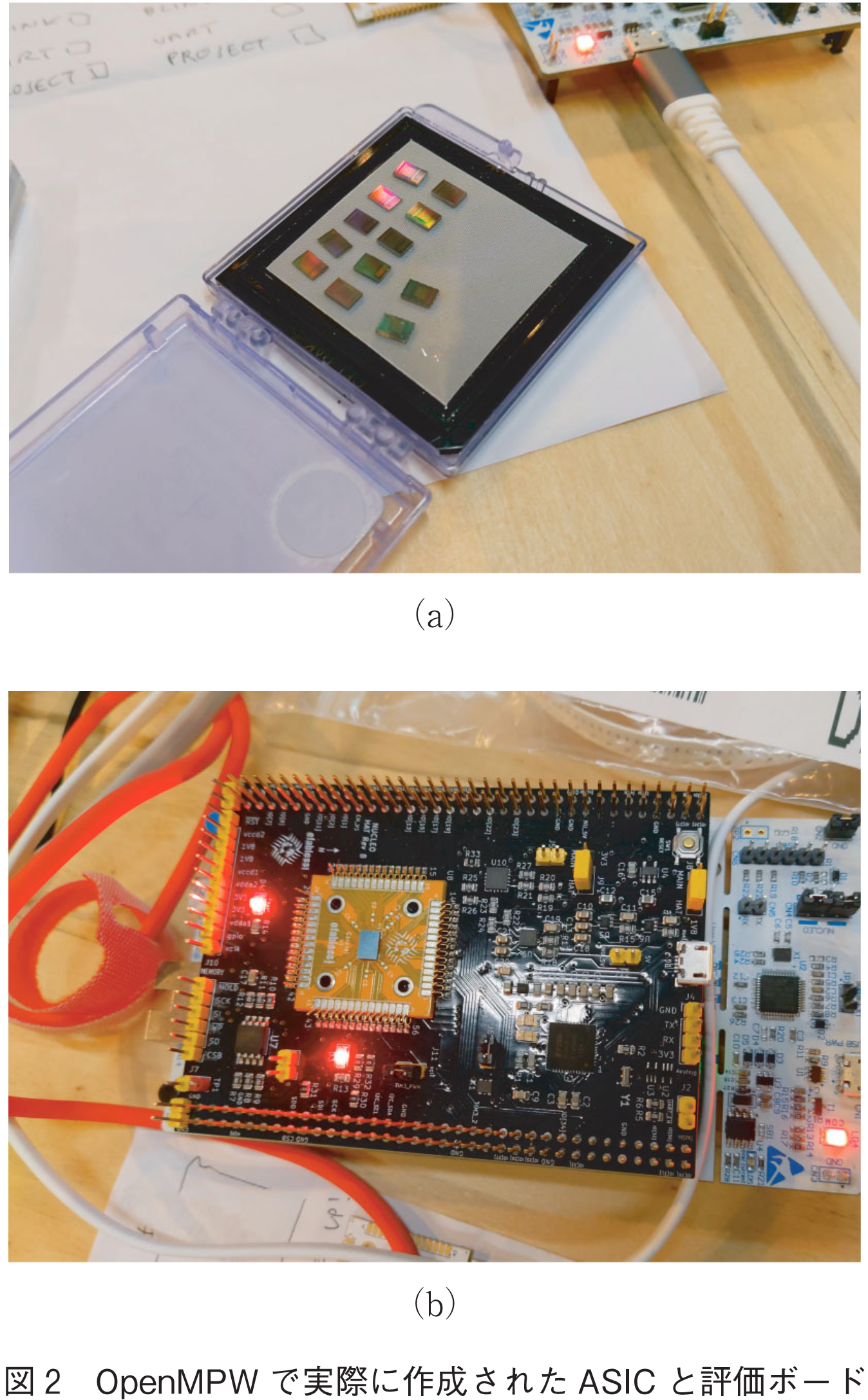

本節では,そのオープンソースPDKムーブメントのプロジェクトを幾つか紹介する.まずは,eFabless社が主催して,Google社が各種支援を行っているOpenMPW(Multi-Project Wafer)(1)がある.このプロジェクトはEDAツール群を統合した統合開発環境を用意し,無料の製造(シャトル)までが準備されたプロジェクトである.このプロジェクトが2020年の11月(2)にスタートしたことで,世界的なオープンソースPDKムーブメントが巻き起こるきっかけとなった(図2).

また,Cadence社とIBM社が主催するオープンソースEDA(3)やIntel社が主催するThe University Shuttle Program(4)などもあるが,情報が公開されていなかったり,大学のみのプログラムであったりとオープンソースPDKムーブメントに乗っているとは言い難いプロジェクトは幾つか存在する.これらのプロジェクトもこのオープンソースPDKの影響を受けて,より民主的に,誰でもアクセスできるような状態となることを期待している.

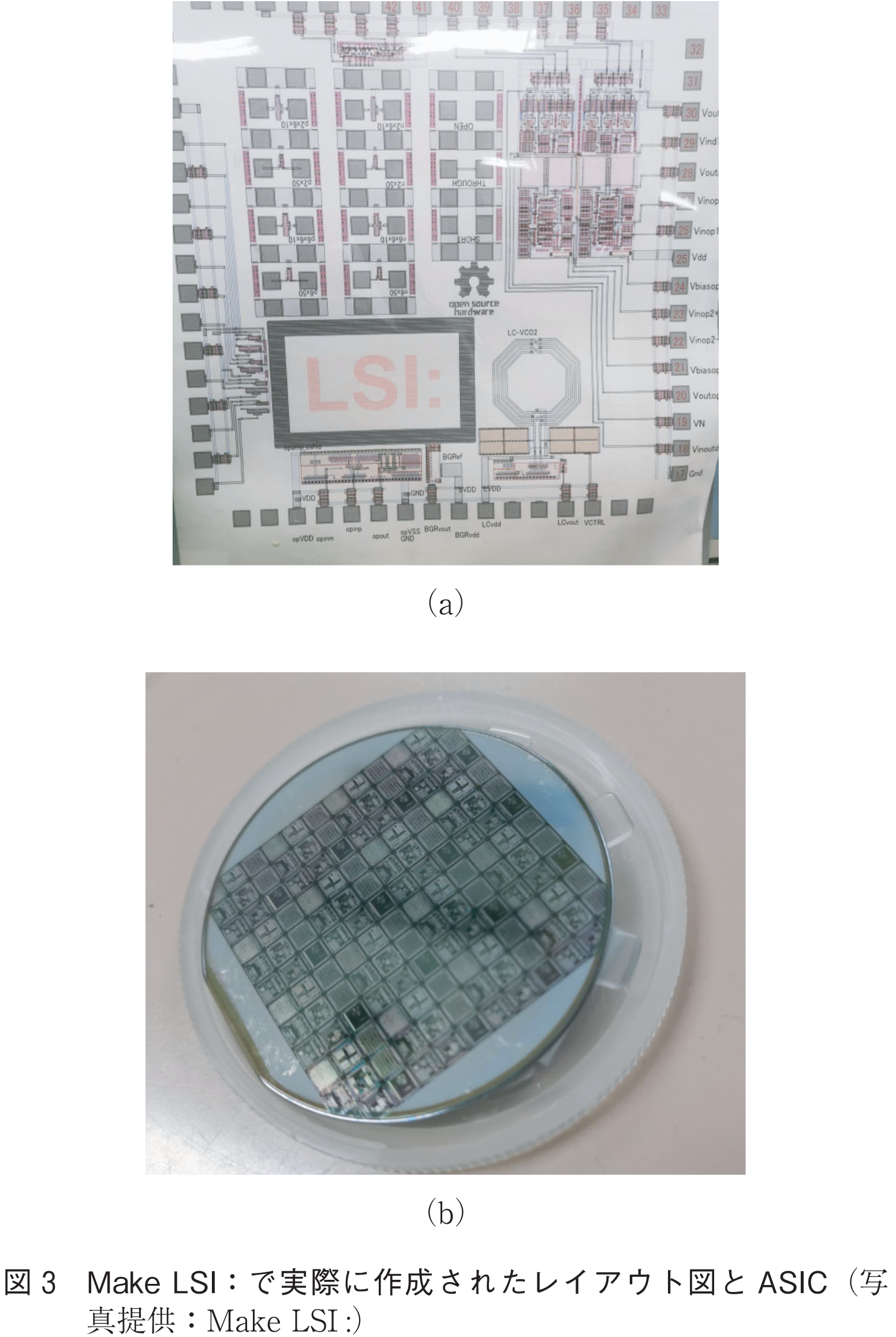

その中で,我が日本においては,OpenMPWより先駆けて2015年から金沢大学の秋田教授とスイッチサイエンス社によるオープンソースPDKムーブメント(5)というべきMake LSI:プロジェクト(6)(図3)の活動がスタートしたのは特筆すべき点である.現在では,より先進的なOpenRule1umPDKプロジェクト(7)として,活動が行われている.これは,本来PDKはファブごとに別物であるが,このPDKを標準化することで,どのファブでも利用可能な標準PDKを作成しようという意欲的なプロジェクトである.

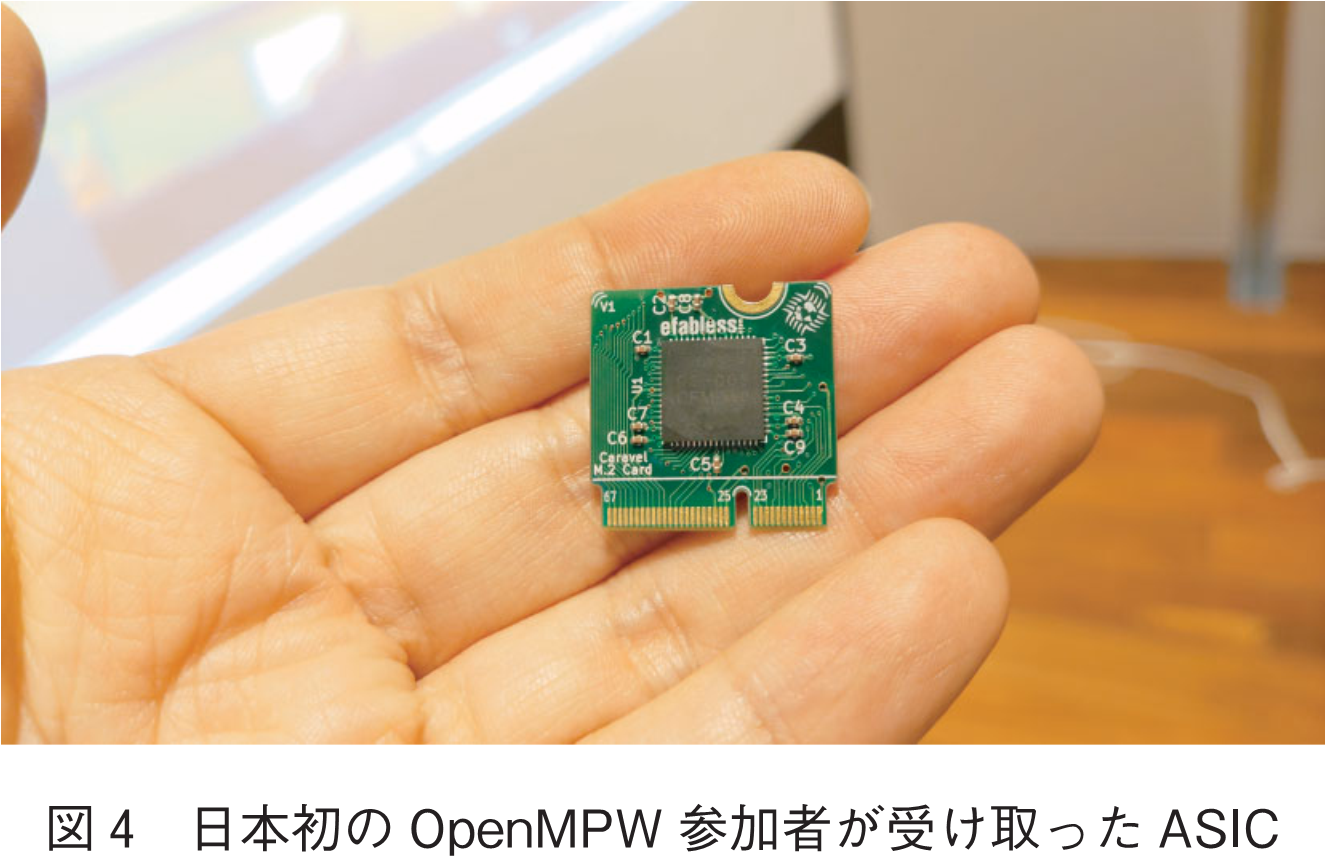

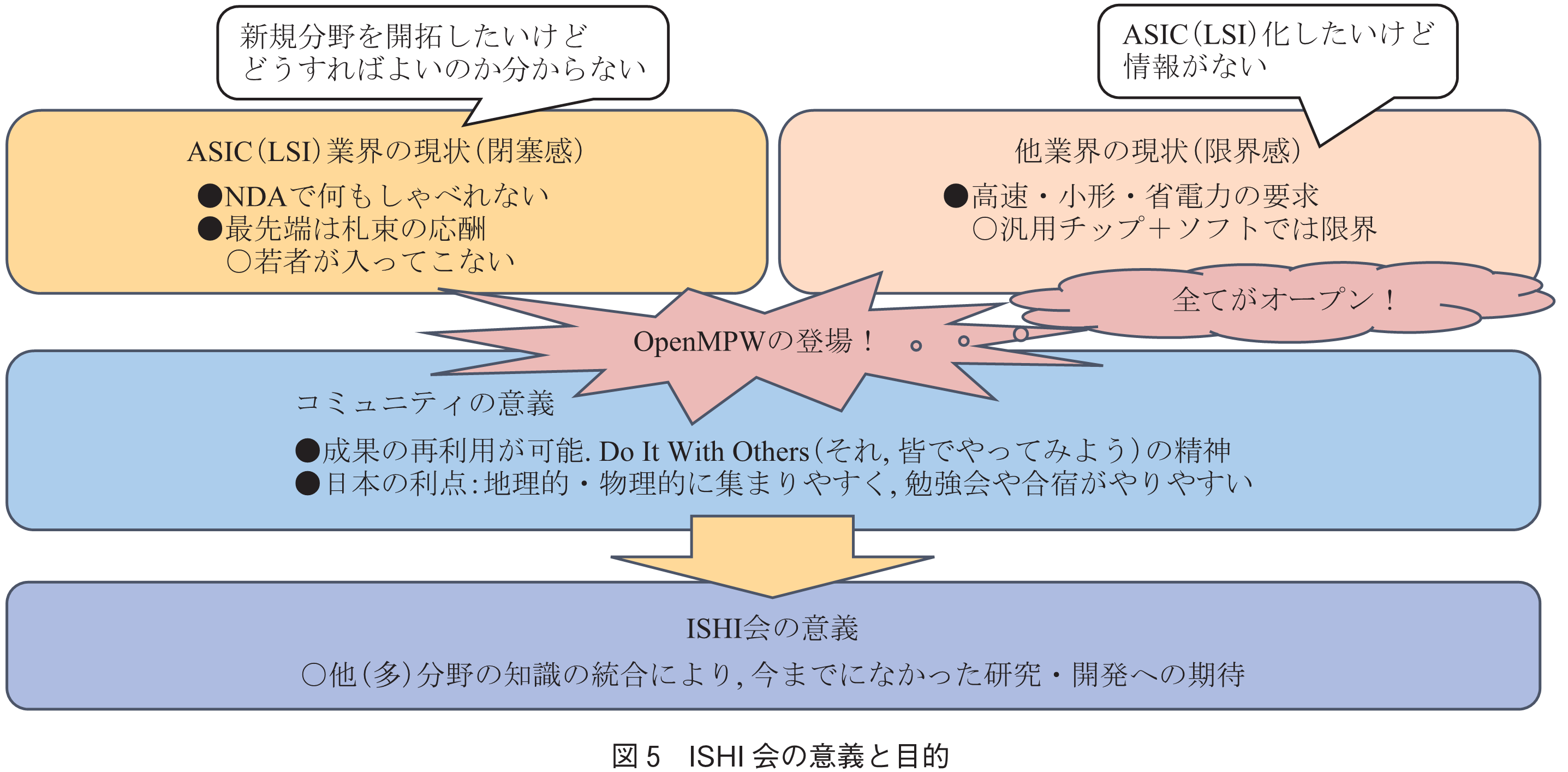

また,このオープンソースPDKムーブメントに合わせて,コミュニティも台頭してきた.まず,OpenMPWの総本山であるOpen Source SiliconのSlackチャンネル(8)が挙げられる.OpenMPWやそれに関わる情報はここに集約されている.続いて,国内であるが,まず,VLSI.jpがある.このコミュニティは日本で最初にOpenMPWに参加し,実際にASIC作成(図4)をした学生たちの手による初心者支援コミュニティである(9).初心者向けの用語解説やOpenMPWのセットアップなどについての記事を執筆・運用している.ほかにも,ISHI会(Inter-linked Society on Homemade IC Kai)がある(10).こちらは,ほかの分野の業界やコミュニティの橋渡しをメインに活動を行っているコミュニティである(図5).そのため,全く半導体に関する知識がない方のための勉強会やハンズオンセミナーを中心に活動を行っている.

以上のように,国内外でオープンソースPDKムーブメントは様々なプロジェクトやコミュニティを巻き込んで,熱い高まりを見せつつある状況である.

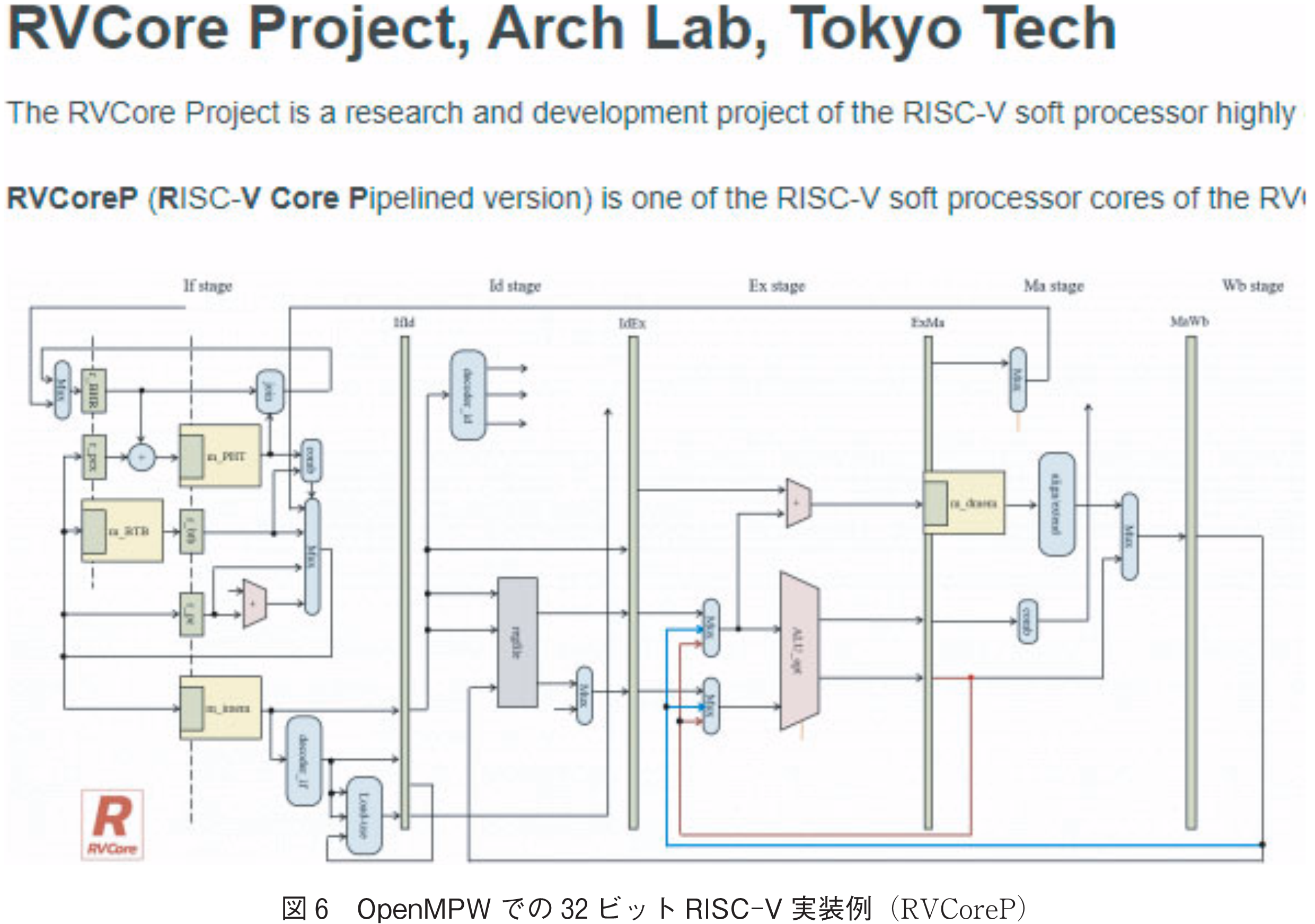

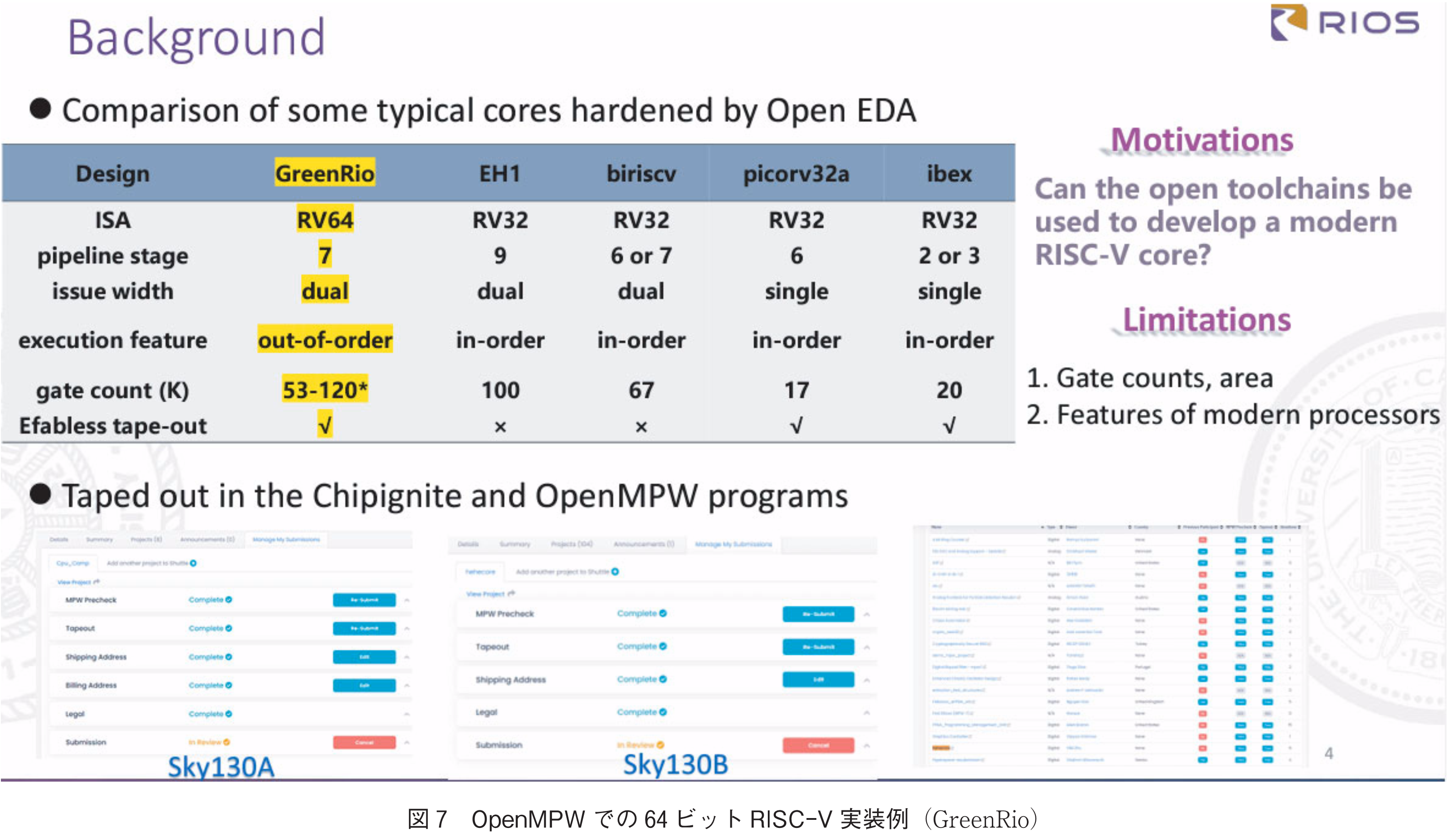

この記事をお読みの読者であれば,次に気になるのはこのオープンソースPDKを利用して,RISC-VコアのASIC作成ができるか?であろう.実は,既に,上記のOpenMPWを利用して,RISC-Vコアを設計し,プロセッサを製造しているプロジェクトがある.例えば,東京工業大学の吉瀬教授による5段パイプラインを採用した32bit RISC-VプロセッサのRVCoreP(図6)(11)やTsinghua-Berkeley Shenzhen Institute(TBSI)の研究チームによるアウトオブオーダを採用した64ビットRISC-VプロセッサのGreenRio(図7)(12)などがある.もちろん,これらのソースコードは全てGithub上に公開されており,誰でも中のソースコードを閲覧したり,他を利用したりすることが可能である.ただ,残念なことにOpenMPWが製造時のトラブルによりデリバリーが1年以上遅れた.そのため,2023年の5月から順次届き始めた段階であり,本稿執筆時の2023年8月ではまだ動作報告などはされていないようである.

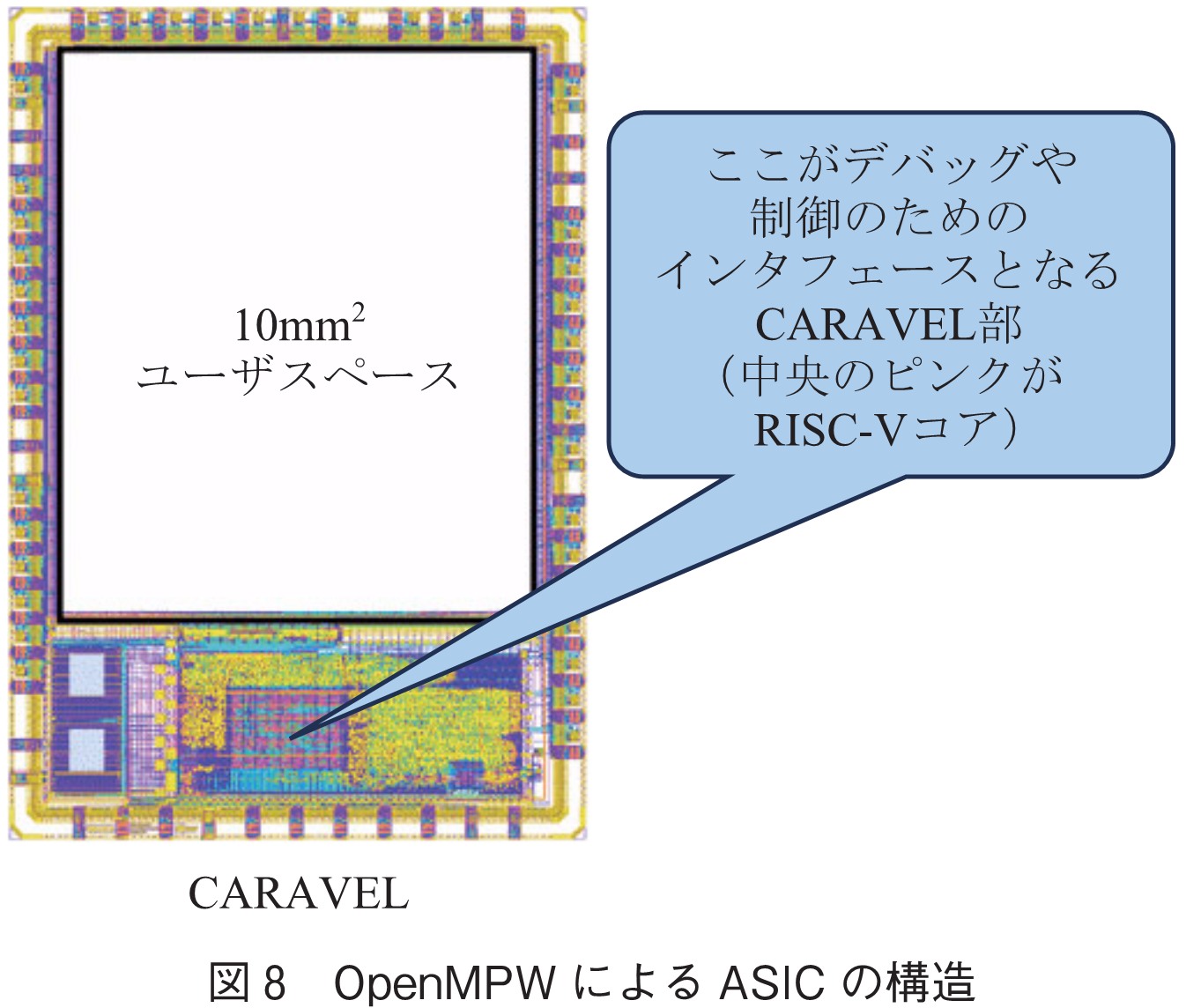

また,OpenMPWで製造できるASICにもRISC-Vプロセッサが載っている.それは,CARAVELと呼ばれるユーザコア用のデバッグや制御を行うための部分となる(図8).ここに制御用のコアとして32bit RISC-Vプロセッサが載っている.この実装は動作しているため,32bit RISC-Vプロセッサであれば十分製造できると考えられる.

本章の最後は,現在のホット分野である生成AIの話である.RISC-Vは多くのHDLによるソースコードが公開されている.すなわち,RISC-Vのソースコードを生成AIで生成したいときの学習データとして大量のHDLを利用できるということであり,RISC-Vは生成AIと非常に相性が良い.(補足:取り扱いには各国のライセンスや同意の問題がある点については注意が必要であるが,日本国内においては利用可能である.)

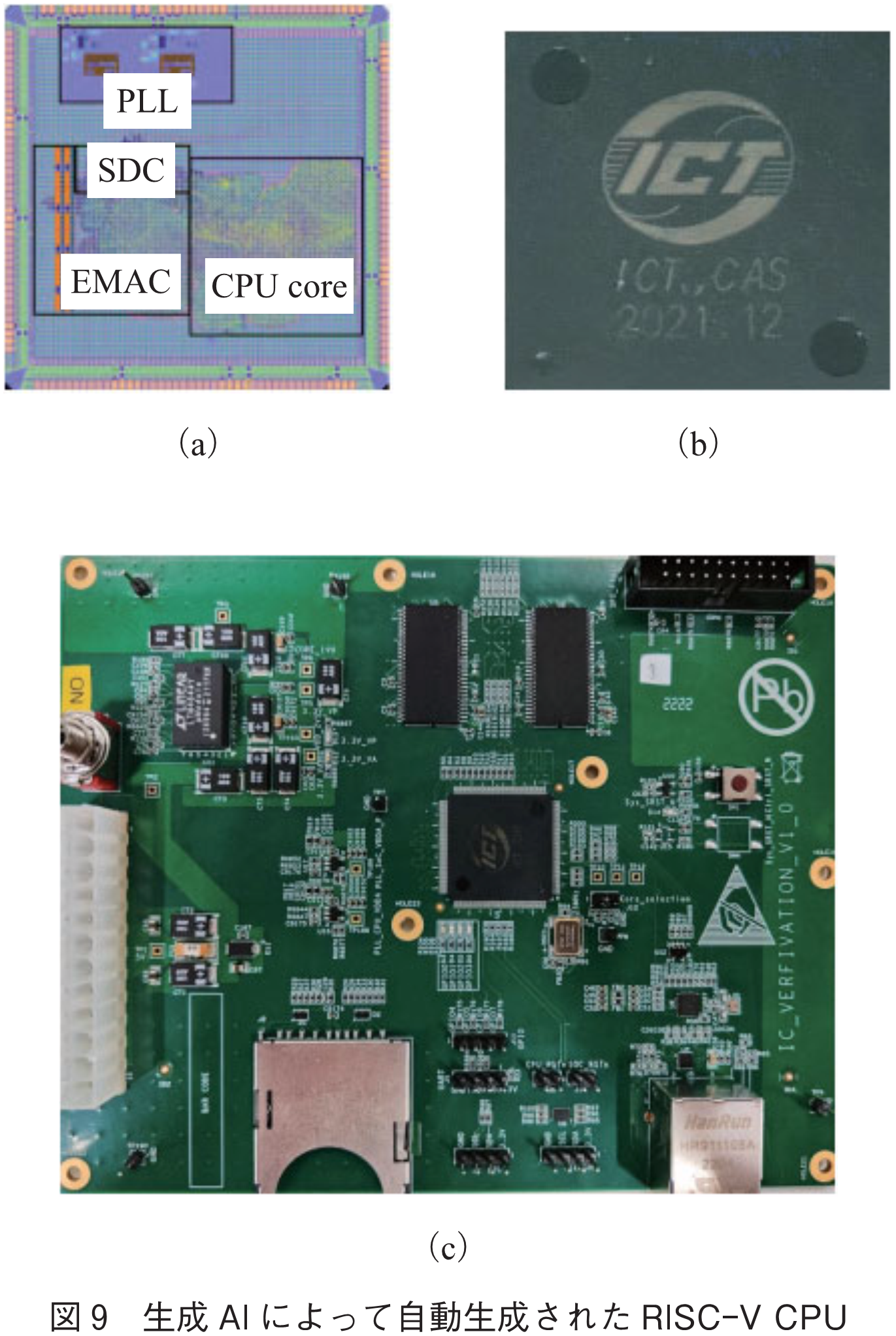

実際に,2023年6月に中国の研究チームにより,生成AIで,RISC-V CPU(図9)をゼロから約5時間で設計し,65nmプロセスで製造し,最大300MHzで動作させたという論文(13)が公開されている.

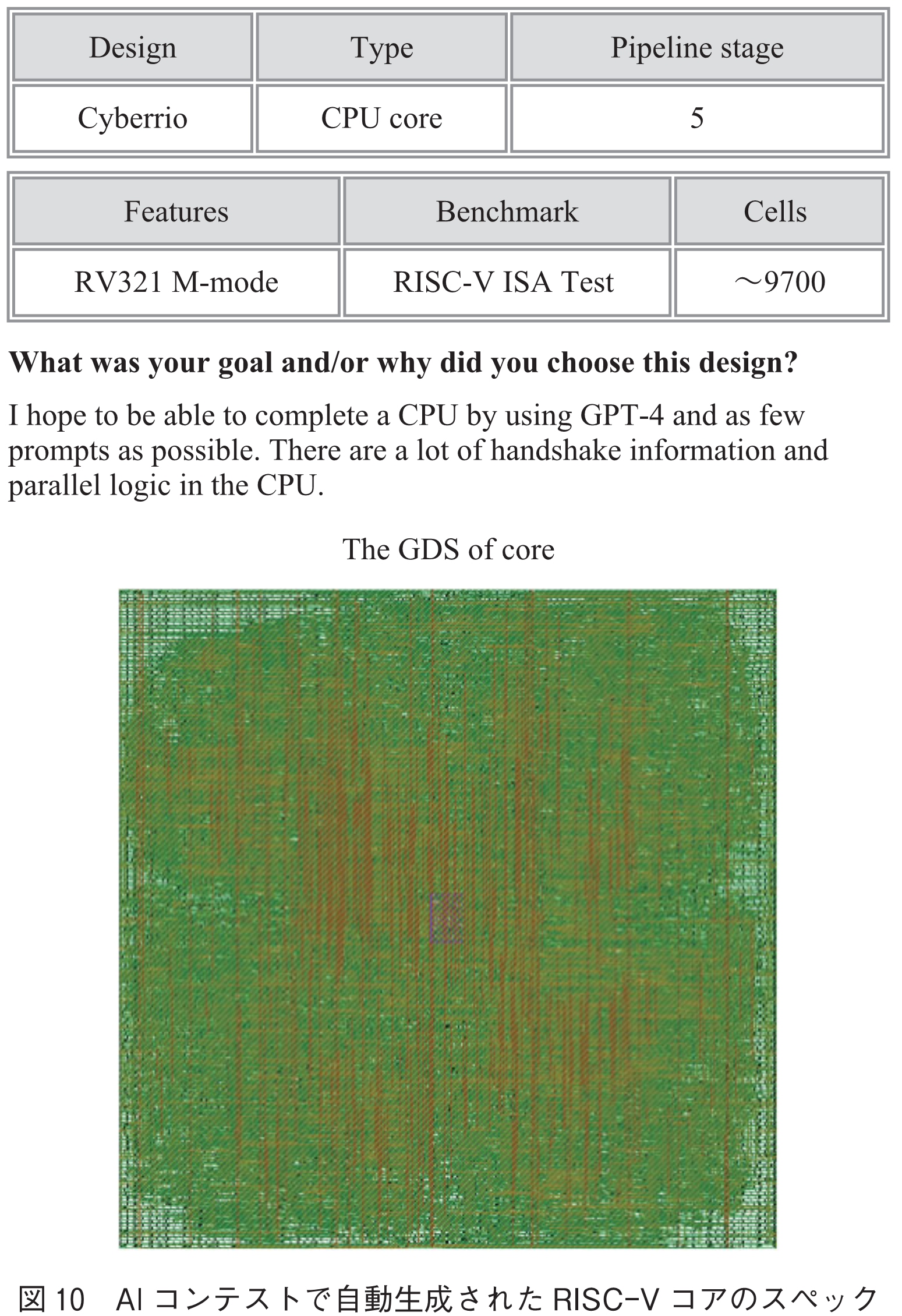

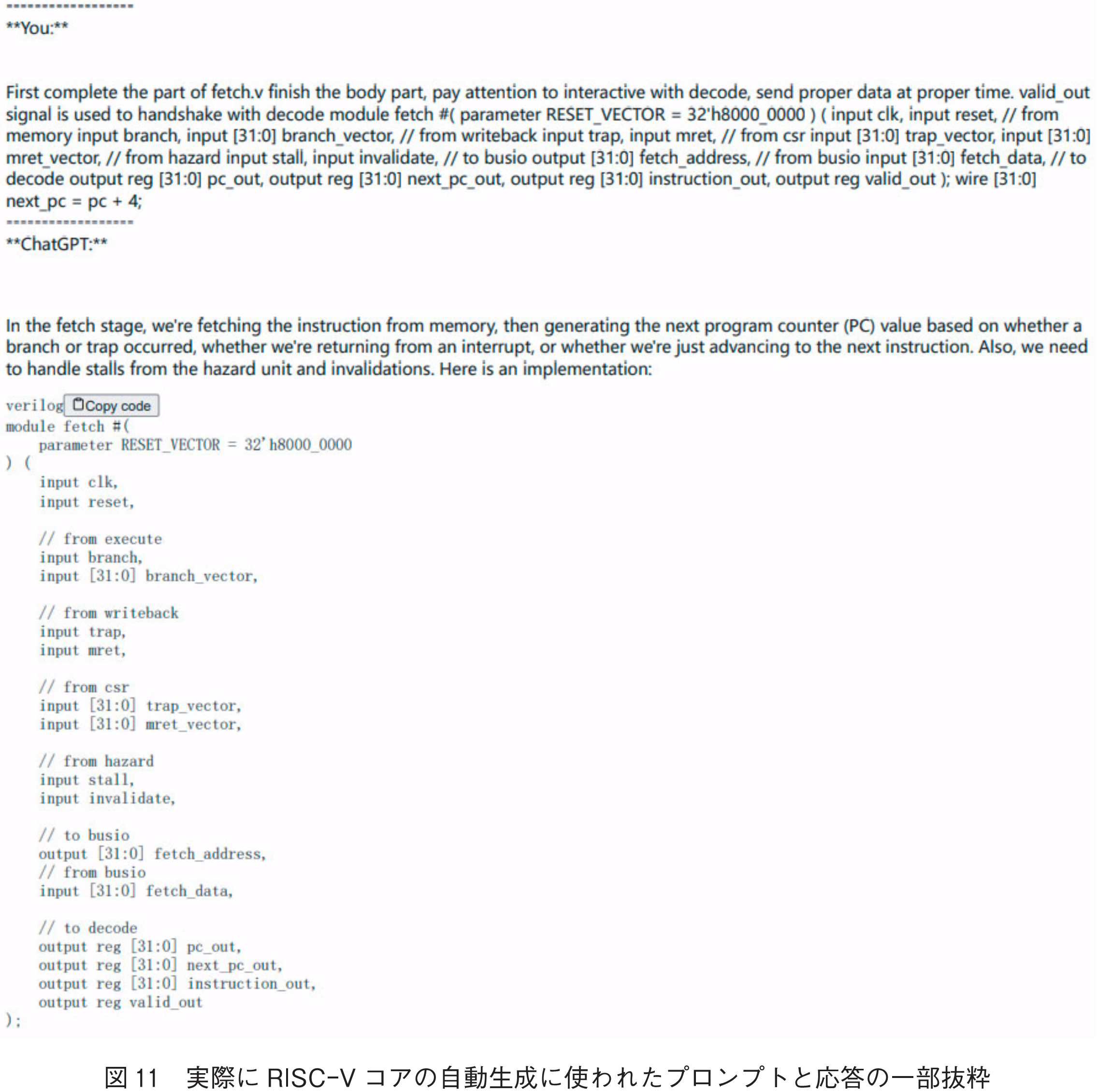

更に,PDKもソースコードが公開されており,理論上はRISC-Vの仕様などからPDKまで含めた最適化をかけることも可能である.そのため,オープンソースPDKムーブメントによる生成AIに可能性を見いだし,eFabless社(OpenMPWの製造担当)が主催でAIコンテスト(14)が開催された.そして,その2nd placeの作品(15)はRISC-V CPU(図10)であった.このコンテストにおいては実際に使われたプロンプトも公開されている(図11)ため,自分でも製造することが可能であるし,それを改良することも可能である.また,それらの新しく作られたソースコードやプロンプトを新しい学習データとして利用することも可能である.

このように,オープンソースPDKムーブメントによるRISC-Vと生成AIは相乗効果で進化していく可能性を秘めており,これからも目が離せない分野である.

前述の米国とEUのファウンドリー工場増設の動きは日本でも同様であり,各工場が稼動を始める時期に稼動率の維持ができなければ投資額が回収できないだけでなく,幾つかの工場の閉鎖が予想される.ファウンドリービジネスは固定費が大きい特徴があり景気変動により一定の稼動率を下回ると倒産しやすい業態であることから,年々淘汰され今は世界で数社に収歛した歴史がある.

そのため,ファウンドリーの稼動率維持のためにファブレス企業によるSoC・ASIC作成の需要を向上させる施策が必要になる.米国とEUのRISC-V活動は本目的に合致しており,SoC・ASICエンジニアの技術力向上と設計された製品の性能向上による市場での競争力強化が産学合同で進んでいる.これには実半導体作成の機会創出による技術蓄積が必要であり,企業のみならず学術機関であるUC BarklayやETH Zurichでは140nmから12nm等のプロセスでRISC-Vの実チップ開発を行っている(16).国内では学術機関がCPUコアからペリフェラルを含めたSoCとして動作可能な半導体開発は,ただの開発とデバッグでありアカデミックではないという理由で避けられることが多いが,それでは産業界と学術機関の要求技術ギャップが解消しないことから,是非米国とEUに追従してほしい.

世の中の多くのRISC-VプロジェクトがHDL作成,若しくはFPGAでの検証までであり,そこから実際のチップ開発に壁がある.これは1.に述べられるようにファウンドリーに合わせたEDAツールが必要という課題がある.有償EDAツールベンダは寡占化が進んでおり,OpenHW Groupでは公開されているRISC-VのHDLから,既存の有償EDAツールを使えるようにすることで課題解決を図っている.そこを一歩踏み出して有償EDAツールベンダに脅威と誤解を受けない形でOpenMPWに見られるオープンソースEDAツールによる半導体作成により国内でノウハウ取得と技術蓄積が進むことを期待する.

前半のRISC-VによるHDLの論理回路設計技術と,1.のEDAツールによる半導体開発は共に広義的にはディジタル技術に属しており,競争力のある欧米の組織は長年の技術蓄積の上に競争力を高めてきた.ディジタル技術分野で日本が技術立国を目指すには同様の施策を取ることが近道である.

国内では論理回路技術者,ソフトウェア技術者等を社内で技術蓄積せず,特に2000年代以降はゼネコン型多重下請けを伴う外注による発注業務の管理によって研究開発や製品開発を行う流れが長く続いている.このこと自体は多くの日本企業が1990年代後半から2000年代に社員数を減らし,収益悪化による倒産を避ける目的では有効であったが,欧米企業と比較したときに日本企業のディジタル技術分野での競争力低下につながっている.最近は外注以外にプロジェクトごとに人員が集まり,プロジェクトが終了したら解散するプロジェクト方式を取り入れるところがあるが,この方法もそのままではチームが解散した時点でチーム活動により得られたディジタル技術が組織から消失する.

ではどうするかであるが,具体的な例を記述したい.ある論理回路を設計している場合,大半の時間は設計自体ではなくデバッグに費やされている.これはLSIアートワークでもソフトウェア開発でも同様である.そしてデバッグを続けているうちにある時点で「動いた!」と技術者は喜ぶ瞬間がある.前述の業務管理による開発スタイルでは,その技術者は即座に次の開発タスクが割り当てられてしまう.実はこれは組織にディジタル技術を蓄積する観点からは非常に悪い業務プロセスである.

それは,「動いた!」と喜ぶ状態の論理回路はデバッグを繰り返して何とか動いた状態であることが多く,その実装を後で本人や他人が利用しようにもやっつけの論理回路設計では再利用ができない.そこで,Software Bill of Materials(SBOM)が生まれた背景と同様に,全体設計を考えて動作が確認できた各部分を部品化(ライブラリ化と同意,以降コンポーネントで統一)を目的に,再利用可能なようにインプット・アウトプット(ソフトウェアではAPI)を整理して内部実装をきれいに書き直し(リファクタリングとも呼ばれる),同じ機能は他で再実装せずに本コンポーネントをそのまま使えるようにする作業を開発中に定期的に取り入れる必要がある.

これによりPDCAサイクルを回していると同様の効果が生まれ,再利用できるコンポーネントがどんどん蓄積する.一見するとリファクタリング中は全く新しい機能の実装が進まないことから非効率に見えるが,実際には次のステップの開発で毎回全てを再実装するのと比較し,多くのコンポーネントを再利用できることで新規開発部分を減らせ,コストダウンと開発速度向上という直接メリットがある.それに加え本手段を継続することで製品の品質が上がる効果がある.それは各コンポーネントを皆で再利用することによりバグ発見につながり,更に良い実装が見つかることが多く,それによりあるコンポーネントを改良すると,該当コンポーネントを活用した全てのプロジェクトが改良の恩恵を受けられからである.従来の日本企業が強かった改善活動と同様の効果をもたらす.

このような開発手段を取る最大の背景は,前述のようにディジタル技術の開発では設計自体に必要な時間よりデバッグの時間が多いという時間効率が非常に悪い欠点を克服するためである.実際,米国の半導体企業,Apple,テスラ等への就職や大学の研究室に所属すると,ソースコード管理サーバに過去から蓄積された多くのコンポーネントに触れることになる.これは大学組織であるUC BarklayやETH Zurichが強力な研究開発能力を持つ一要因である.

さてここで紹介した開発手段を実際に実行するには,ソフトウェア開発で用いられるContinuous Integration/Continuous Delivery(CI/CD)に似た経験と各コンポーネントの知財やライセンスの取扱いの知識が要求される.したがって米国においてもカリフォルニアのテック系企業の自動車やロケット開発が,歴史ある米国の自動車企業やロケット開発組織より製品開発サイクルが早い要因となっている.

RISC-Vに取り組む目的は,ISAの設計がきれいであるから,オープンであるから,マーケティング力があるから等の表面上の事象にとらわれることなく,今一度半導体業界全体をとらえた地味で継続的な技術開発を続けることで,ディジタル技術分野をほぼ全て輸入せざるを得ない今の日本の現状を改善し,いつかは輸出で稼ぐ時代に変革したい.

RISC-Vアーキテクチャは,オープンなISAとして,従来の命令セットと異なり,自由に設計・製造ができる特性を持つ.その起源,技術的特徴,国内外での動向,そしてRISC-V Internationalの役割は多岐にわたる.オープンソースPDKムーブメントとの結びつきを通じて,RISC-Vは半導体製造の民主化にも寄与している.

世界的には,ファウンドリー工場の増設の動きがあり,RISC-Vの活動はその稼動率維持に一役買っている.特に米国とEUでは学術機関がRISC-Vのチップ開発を積極的に進めているが,日本にはその追随が求められている.技術蓄積の観点から見れば,欧米の競争力は長年の技術の蓄積に基づいているが,日本の多くの企業は外注やプロジェクトベースの開発により技術蓄積に障壁が存在する.技術の再利用やデバッグの取組みを通じて,技術蓄積の加速が必要である.

結論として,RISC-Vの導入とそのアーキテクチャの活用は,単に新しい技術としての採用にとどまらず,日本のディジタル技術分野における国際競争力の向上と技術輸出の推進に重要である.私たちは本技術開発に継続的に取り組んでいく所存である.

(1) OpenMPW Program.

https://efabless.com/open_shuttle_program

(2) 2020年11月に最初のシャトルがスタート.

https://platform.efabless.com/projects/shuttle/1

(3) 日経クロステック,「オープン・ソースEDA」のWWWサイトが誕生,米Cadence社と米IBM社,UCLAがソース・コードを提供.

https://xtech.nikkei.com/dm/article/NEWS/20080305/148472/

(4) HPC, Intel Is Opening up Its Chip Factories to Academia.

https://www.hpcwire.com/2022/10/06/intel-is-opening-up-its-chip-factories-to-academia/

(5) 金沢大学の秋田教授によるMake LSI:.

https://fabcross.jp/news/2015/07/20150717_switchscience_and_kanazawa_univ.html

(6) Make LSI: .

https://scrapbox.io/makelsi/

(7) OpenRule1umPDK.

https://github.com/MakeLSI/OpenRule1um

(8) Open Source SiliconのSlackチャンネル.

open-source-silicon.slack.com

(9) VLSI.jp (日本で最初にOpenMPWに投稿した学生によるサイト).

https://vlsi.jp/

(10) ISHI会(純粋なユーザコミュニティ).

https://ishi-kai.org/

(11) RVcore Chip1.

https://platform.efabless.com/projects/1293

(12) GreenRio.

http://riscv.or.jp/wp-content/uploads/day3_TsingHua-University_riscv_day_yifeizhu_final.pdf

(13) S. Cheng, P. Jin, Q. Guo, Z. Du, R. Zhang, Y. Tian, X. Hu, Y. Zhao, Y. Hao, X. Guan, H. Han, Z. Zhao, X. Liu, L. Li, X. Zhang, Y. Chu, W. Mao, T. Chen, and Y. Chen, “Pushing the limits of machine design: Automated CPU design with AI,” 2023.

https://arxiv.org/abs/2306.12456

(14) AI-Generated Open-Source Silicon Design Challenge.

https://efabless.com/ai-generated-design-contest

(15) Cyberrio.

https://github.com/hello-eternity/Cyberrio

(16) PULP Silicon Proven designs.

https://pulp-platform.org/implementation.html

(2023年11月15日受付)

オープンアクセス以外の記事を読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード