|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

量子コンピュータにおける回路とシステム

小特集 2.

量子技術に着想を得たCMOSアニーリングの概要と量子/CMOSアニーリングの普及に向けた取組み

Overview of CMOS Annealing Inspired by Quantum Technology and Efforts towards the Popularization of Quantum/CMOS Annealing

Abstract

社会課題の解決には様々な最適化問題を解く必要がある.組合せ最適化問題を高速に解くと期待されているのが新しいコンピューティング技術であるアニーリングマシンである.CMOSアニーリングはその一つであり,本稿ではその概要を説明する.また,新しいコンピューティング技術を普及させるために,Annealing Cloud Webという初学者向けのWebサイトを運営する取組みがあるため,それについても紹介する.

キーワード:CMOSアニーリングマシン,組合せ最適化,Annealing Cloud Web

近年,社会課題は複雑化しており,物流の効率化や交通渋滞の解消など様々な課題を解決する必要がある.課題の解決には多くの場合最適化問題を解く必要がある.社会課題の複雑化に伴い,最適化問題,特に組合せ最適化と呼ばれる問題は,解の候補が爆発的に増大し,従来のコンピュータで解くのは困難になりつつある.そこで,組合せ最適化問題を効率的に解くための新しいアルゴリズムが提案されている.特に量子効果を用いた量子アニーリングという手法が提案され,更にはその量子アニーリングに着想を得たアニーリングマシンやイジングマシンと呼ばれる技術が提案されている.その技術の一つであるCMOSアニーリングマシンも,半導体技術を効率的に活用した新しいコンピューティング技術であり,現在では,ハードウェア技術のみならず,これをうまく使いこなすソフトウェア技術の研究も現在進行形で進められている.本稿では,量子に着想を得た技術の概要を紹介し,量子含めた新しいコンピューティング技術の普及に向けた取組みについて紹介する.

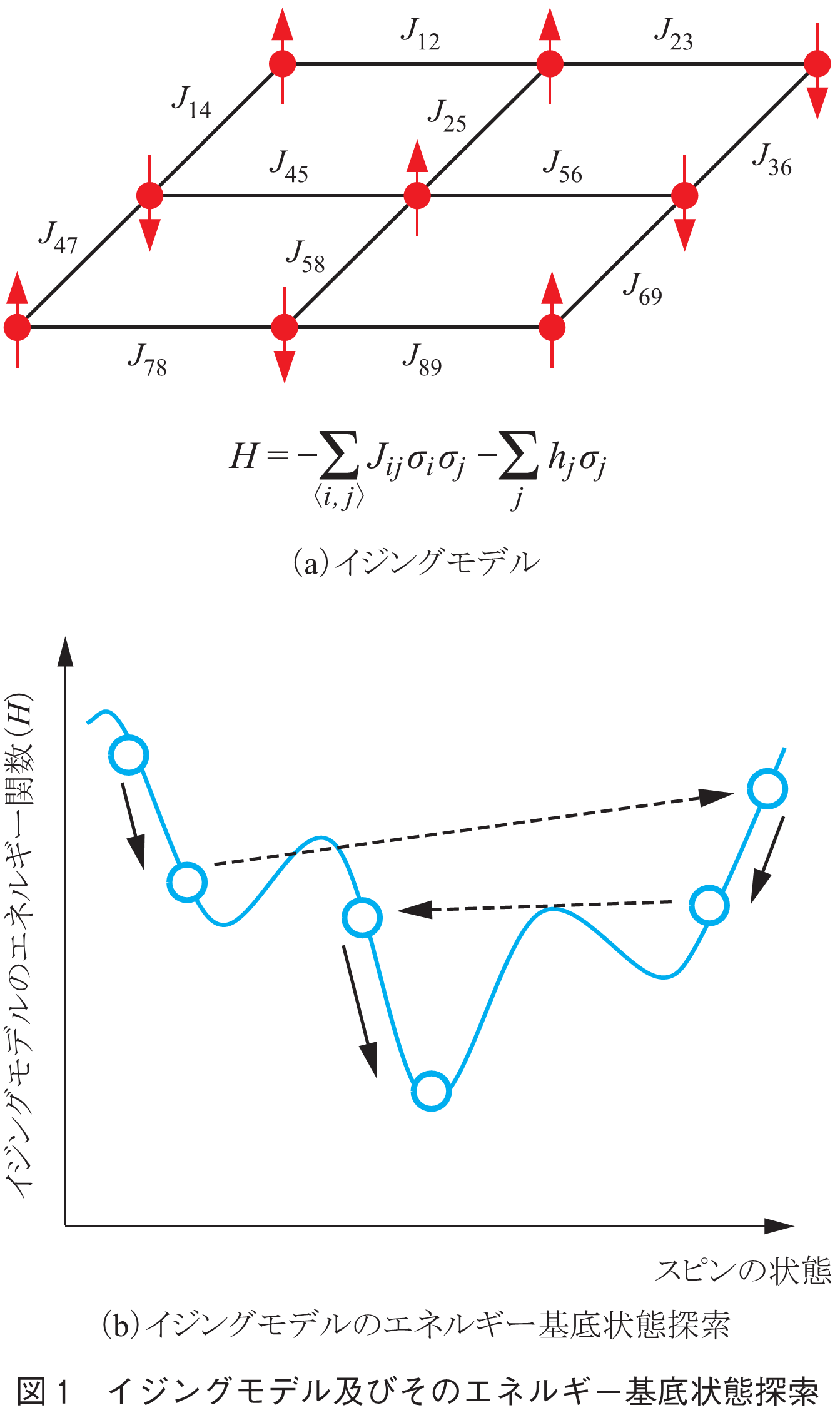

アニーリングマシンとは,磁性体の振舞いを表す統計力学上のモデルであるイジングモデル(図1(a))を用いて組合せ最適化問題を効率的に解く新しいコンピューティング技術である.その代表的な例がD-Wave社の量子技術を用いた量子アニーリングである(1).量子アニーリングマシンでは,量子効果を活用してイジングモデルのエネルギーの基底状態におけるスピン状態を求める.

この量子アニーリングに着想を得て,必ずしも量子効果を用いていないが同様にイジングモデルを使って最適化問題を解く技術が多数提案されている.その一つが,半導体回路を用いてイジングモデルを模擬するCMOSアニーリングマシンである(2),(3).CMOSアニーリングマシンでは,イジングモデルの基底状態探索を行うためCMOSアニーリングという半導体ハードウェア上での最適解の探索を効率的に実行するアルゴリズムを用いる.このアルゴリズムは,シミュレーティドアニーリングというアルゴリズムを,半導体ハードウェア向けに応用した手法と言える.量子アニーリングとCMOSアニーリングを定性的に比較すると,量子効果を用いている量子アニーリングの方が最適化問題の求解の精度は高いと言える.一方,CMOSアニーリングは半導体回路を用いているため,動作の安定性と拡張性に優れていると言える.

続きを読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード