|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

|

電子情報通信学会 - IEICE会誌 試し読みサイト

© Copyright IEICE. All rights reserved.

|

量子コンピュータにおける回路とシステム

小特集 1.

シリコン電子スピン型量子コンピュータ開発

Development of Silicon-based Electron Spin Quantum Computer

Abstract

近年,IBM,Googleによる超伝導型量子コンピュータの開発により,量子コンピュータへの関心が高まっている.量子コンピュータは,古典的な“0”,“1”の情報のみならず,それらの重ね合わせの状態の情報をも一つの量子ビットで表現できる能力を有しており,社会問題解決の効率的なソリューション実現への期待が高まっている.本稿では,量子コンピュータの概説とともに,現在開発推進中のシリコン大規模量子コンピュータの実現に期待の高まるシリコン電子スピン型量子コンピュータの開発,特に,極低温量子ビット制御方式の開発について述べる.

キーワード:量子コンピュータ,シリコン電子スピン型,極低温,量子ビット制御方式

近年,IBM(1),Google(2)による超伝導型量子コンピュータの開発,理研の量子コンピュータ国内クラウド開始など(3),量子コンピュータに関する関心が高まっている.量子コンピュータは,情報を古典的な“0”,“1”の情報のみならず,それらの重ね合わせ状態の情報も一つの量子ビットで表現できる能力を有しており,量子コンピュータを用いた演算により,社会問題解決の効率的なソリューション実現への期待が高まっている.量子コンピュータは,古典コンピュータでは実現できない,いわゆる「量子超越性」を秘めているが,量子コンピュータ自体は,まだまだ開発のれい明期にあると考えられている.本稿では,量子コンピュータの動向を説明するとともに,大規模量子コンピュータの実現に期待の高まるシリコン電子スピン型量子コンピュータの開発状況について述べる.

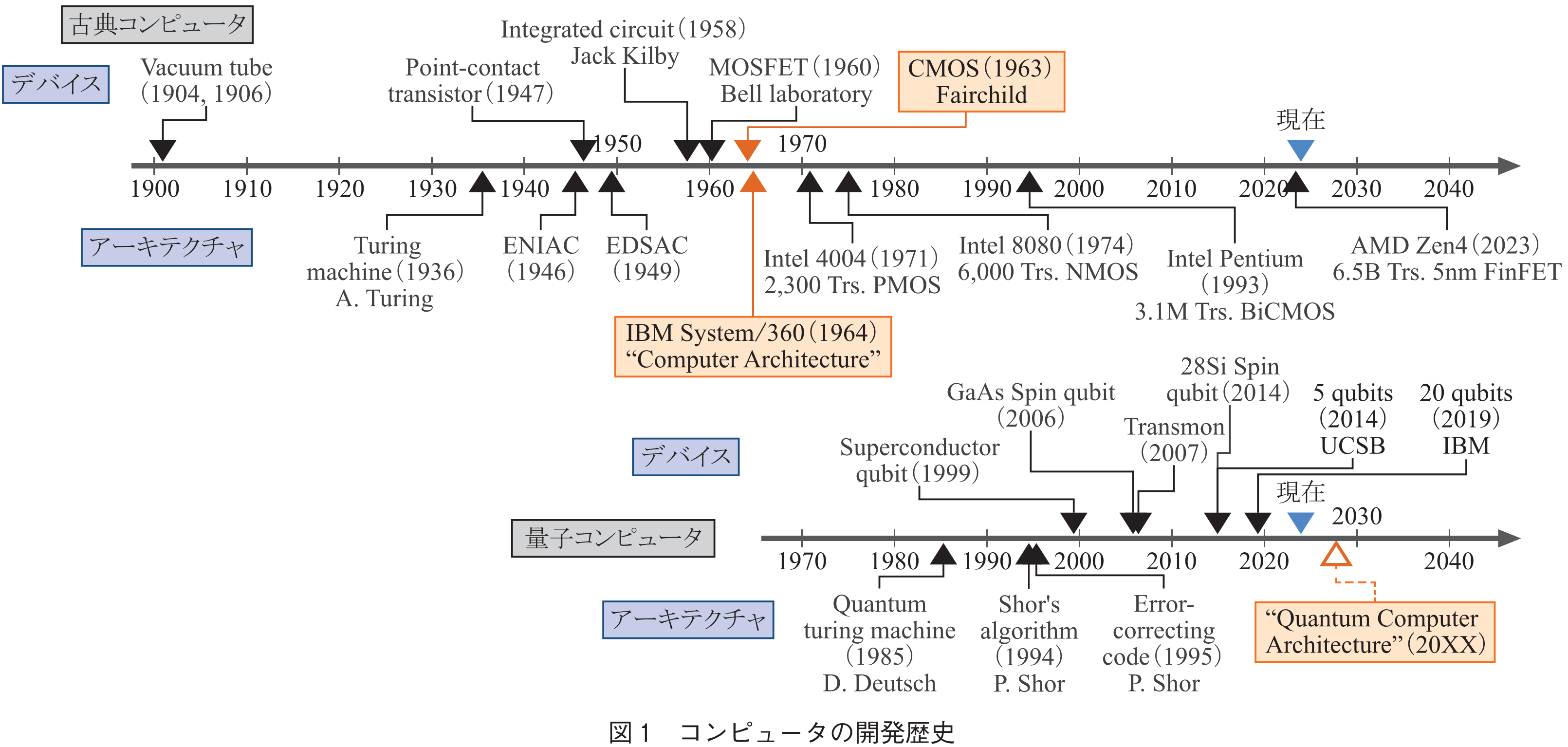

コンピュータの開発歴史を図1に示す.古典コンピュータの開発は,要素部品としての真空管の開発(1904年)からおよそ半世紀後の1940年代ENIACの開発(1946年)に始まる.その後,半導体トランジスタの発明(1947年),及び,その10年後の集積回路の発明(1958年),MOSFETの発明(1960年)を経てコンピュータの心臓部となるCPUの発明(1971年)で基本的構造が作られたのち,半導体の集積度向上により,コンピュータアーキテクチャの刷新が繰り返され,6.5Bトランジスタを集積した5nm FinFETテクノロジーのCPUが量産されている(4).

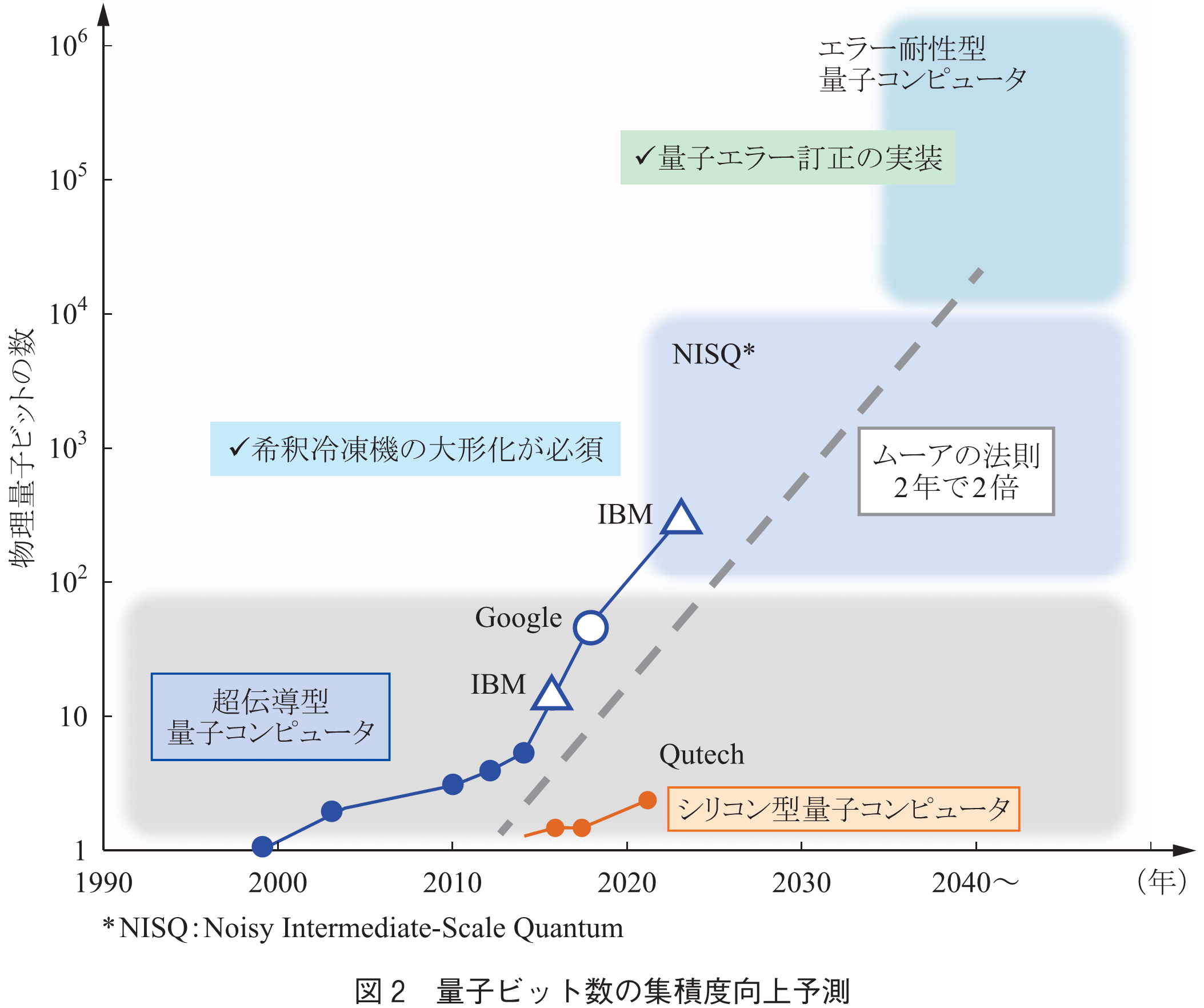

一方,量子コンピュータは,1981年にR.P. Fynmannによる量子コンピュータの可能性についての講演に始まり(5),1985年のD. Deutschによる量子チューリングマシンの発表,1994年のP. Shorの因数分解アルゴリズムに代表される理論面が先行した.その後,超伝導型の量子ビットの開発が成功し(1999年),様々な量子ビットの候補が理論及び実験で報告されるようになった.近年も,IBM社の433量子ビットを搭載した量子コンピュータが報告された(1).量子コンピュータは,概念提唱から40年ほど,実際の量子デバイスが誕生してから25年程度が経過し,現在はまさに,量子コンピュータのれい明期であると言える.量子コンピュータは,量子アニーリング型と,量子ゲート型に大別され,歴史的には,量子アニーリング型が先行開発されてきた(図2).後者の量子ゲート型は,量子ビットに対する演算について,汎用的な論理の設定が可能であり,より複雑な問題に対するソリューションとして期待されている.

このように期待の高まるゲート型量子コンピュータでは,多数の量子ビットを用いて多数回の量子演算を実施することが量子アルゴリズムの観点から必要になるが,そのためには,個々の量子ビットの演算エラーを限りなく0に近づける必要がある.しかしながら,現在,実用化されている量子ビットの演算のエラー率は比較的に高く,高度な量子アルゴリズムの実装は現時点では困難とされている.最終的には,エラー耐性を有した量子コンピュータの実現を目指すが,その実現の前に,中規模な量子ビット数で,かつ,その量子演算エラー率がある程度高くても実用に生かすNISQ(Noisy Intermediate-Scale Quantum)という概念が提唱され,近年重要視されている(6).

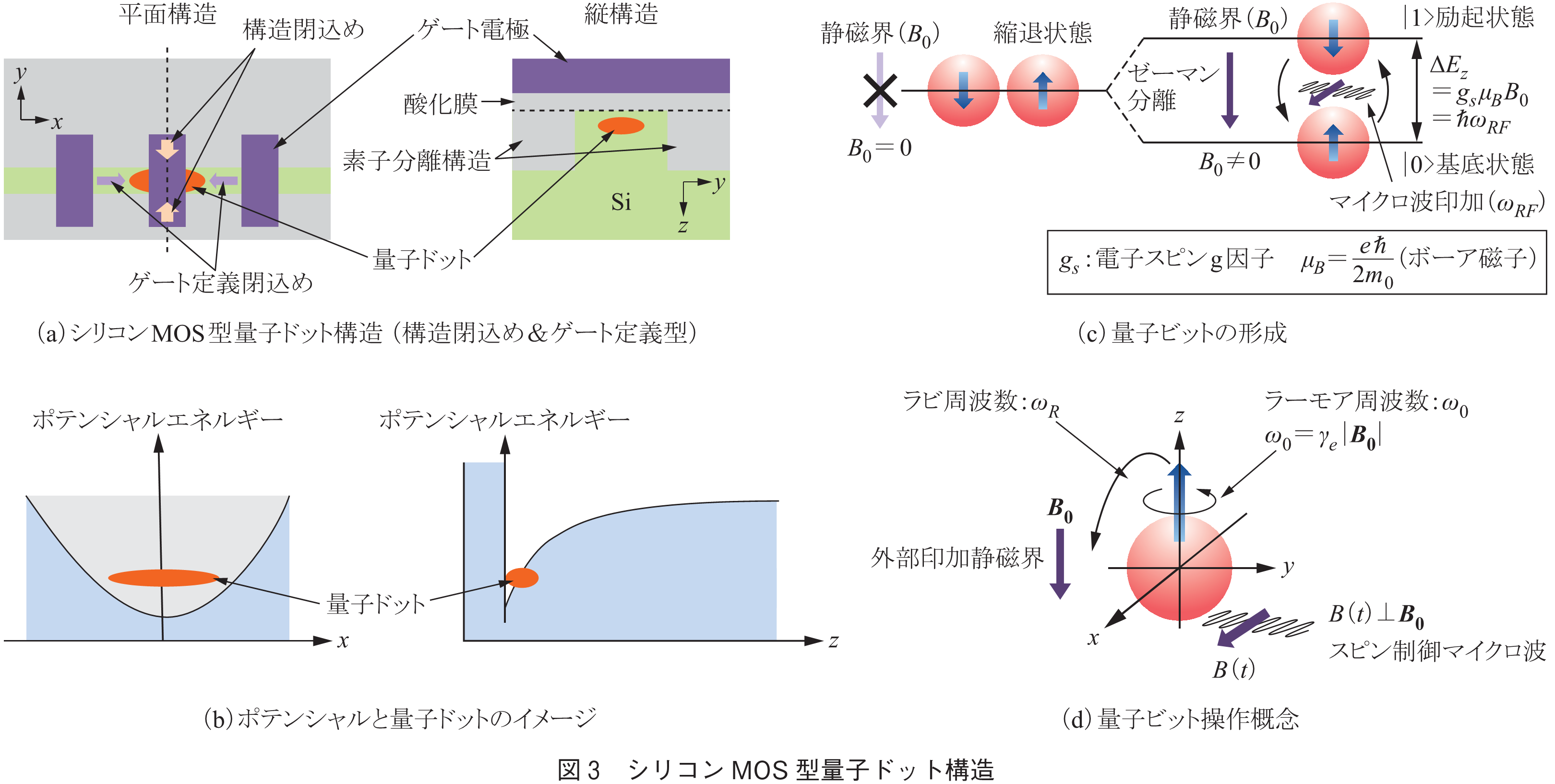

シリコン電子スピン型量子ビットは,スケーラビリティ及び長いコヒーレンス時間の実現に有望とされている.我々は,この方式での量子コンピュータの実現を目指して研究開発を進めている(7).シリコン半導体の電子を量子ビットとする方式は幾つか提案されているが,ここでは,構造閉込めとゲート電位によるゲート定義閉込めを活用した方法について説明する.通常のMOSFETを設計するように,Siのチャネルに相当する部分(不純物のドーピングは実施しない)と,酸化膜による絶縁層を用いて,電子の流れる場所を確保するとともに,量子ドットを形成する場所のゲート電極と,その脇のゲート電極の電位差を設けて,電子を閉じ込める「箱(量子ドット)」を形成する.

図3にその構造とポテンシャル及び量子ドット形成のイメージを記す.MOSFETはゲート酸化膜近傍にバンドベンディングが起こり,電荷の移動が可能になるチャネルが形成されることが知られている.この酸化膜近傍に,構造的,または,電位的に電荷を閉じ込める構造をもたらすと,調和振動子型のポテンシャルが形成され,量子ドットができることが知られている(8).シリコン電子スピン型量子コンピュータは,この量子ドットに電子を1個閉じ込めて,その電子のスピンと呼ばれる自由度を利用して量子ビットとして用いて演算を実現させる.具体的には,量子ドットに電子を閉じ込めた状態で外部から静磁界を印加し,電子のスピンを上向きと下向きの2値の状態に分裂させ,その電子の二状態間を遷移する共鳴周波数をマイクロ波で印加して状態遷移を起こす原理を用いる.

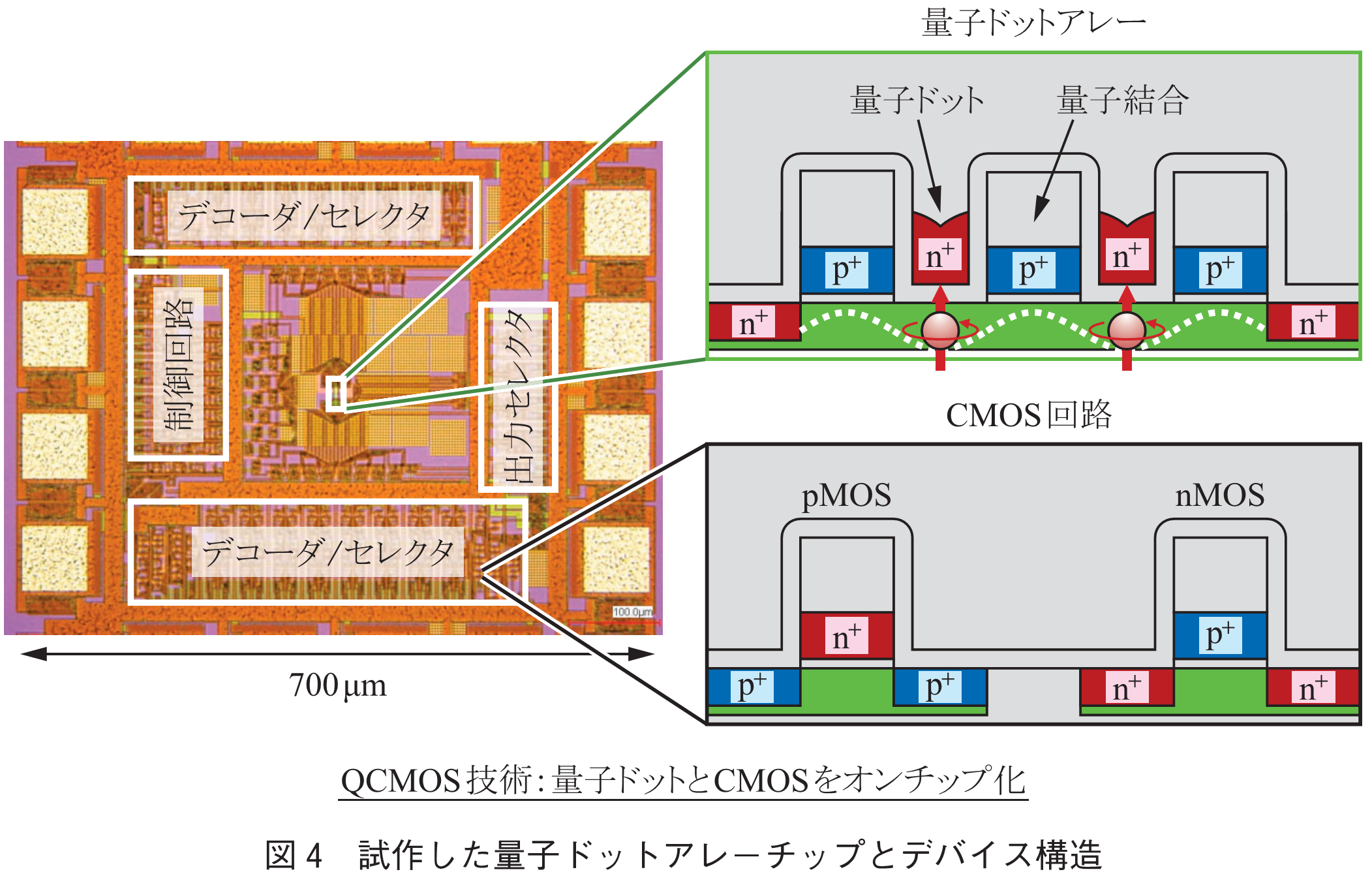

図4は,開発した128量子ドットを搭載した量子ドットアレーチップである(9).これは,量子ビットの評価に先立ち,量子ビットを格納する量子ドットの評価を目的としたチップである.このチップは,量子ドットと周辺回路を同時に集積するQCMOS技術にて設計した.量子ドット部及び,CMOS部の構造も併せて示す.このチップを用いて複数の量子ドットにおける電流量子化の特性を取得した.その後,別のチップを用いて,電子の量子ドット間移動(Single Electron Router)技術(10)及び,量子ドットに格納された電子数を高精度に検出する電荷センサ技術(11)も確立しつつある.更に,量子ドットに格納した電子のスピン状態を制御する際に重要となる,電子スピンのラビ振動の計測にも成功しており(12),これらの技術の完成度を上げていくことが今後の課題となる.

シリコン電子スピンを用いる量子ビットは,熱揺らぎ等の影響を極力避ける必要がある.量子ドットアレーチップは,100mK以下の極低温環境下に設置される.極低温環境は,希釈冷凍機で実現される.真空容器の中で,4Kまで冷却する機構(パルス管冷却装置)と,4Kから100mK以下へ冷却する機構(希釈冷凍機)のメカニズムの異なる二つの冷却機構による階層構造にて実現される.希釈冷凍とは,100mK以下の温度への主たる冷却機構であり,ヘリウムの二つの同位体3He,及び,4Heをそれぞれ液化し,4Heへ3Heを混合する際の希釈熱を利用する冷却機構である.更に,放射熱の影響を除去するために複数のシールド用隔壁で仕切られた構造をしている.シリコン電子スピン型量子ビットを制御するためには,希釈冷凍機を用いた階層型極低温エレクトロニクスシステムを構築中である(7),(13).

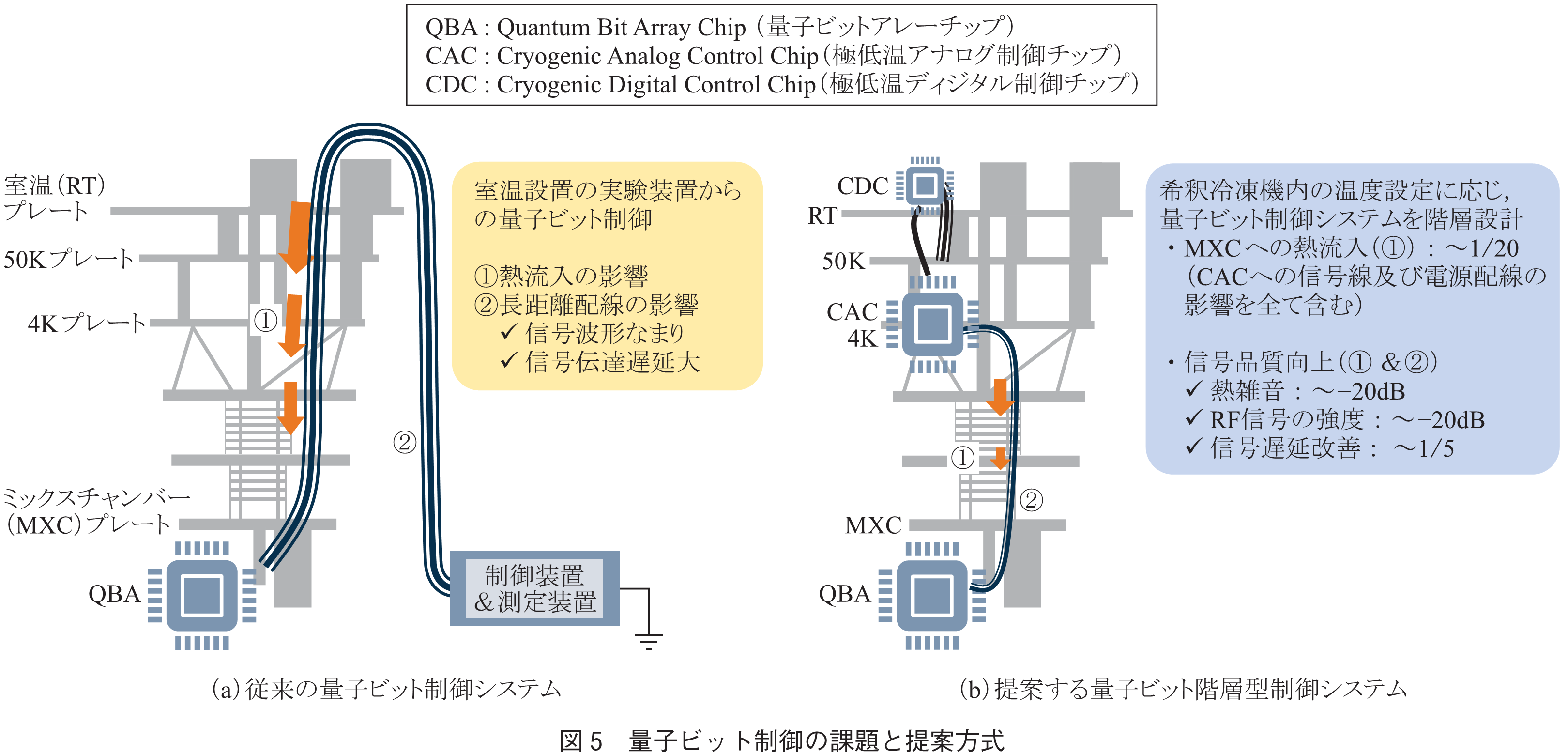

希釈冷凍機の最冷却部に搭載した量子ドットアレーチップを,室温に設置した装置から制御する場合には,図5に示すような課題がある.まず,室温からの熱の流入の問題が挙げられる.多数の量子ビットを制御する場合,量子ビット数に応じて信号本数が増大してしまう.信号線を介して熱の流入及び雑音の印加が懸念される.次に,長距離配線の問題がある.希釈冷凍機の極低温部までは,室温の制御装置から非常に長い配線が必要になる.長距離配線では,伝送自体での熱雑音,信号のスルーレートなどの劣化,信号遅延について課題が生じる.また,そもそも,希釈冷凍機から室温部に取り出せる配線本数にも制限がある.階層型極低温エレクトロニクスシステムはこれらの課題を解決することを目指している.

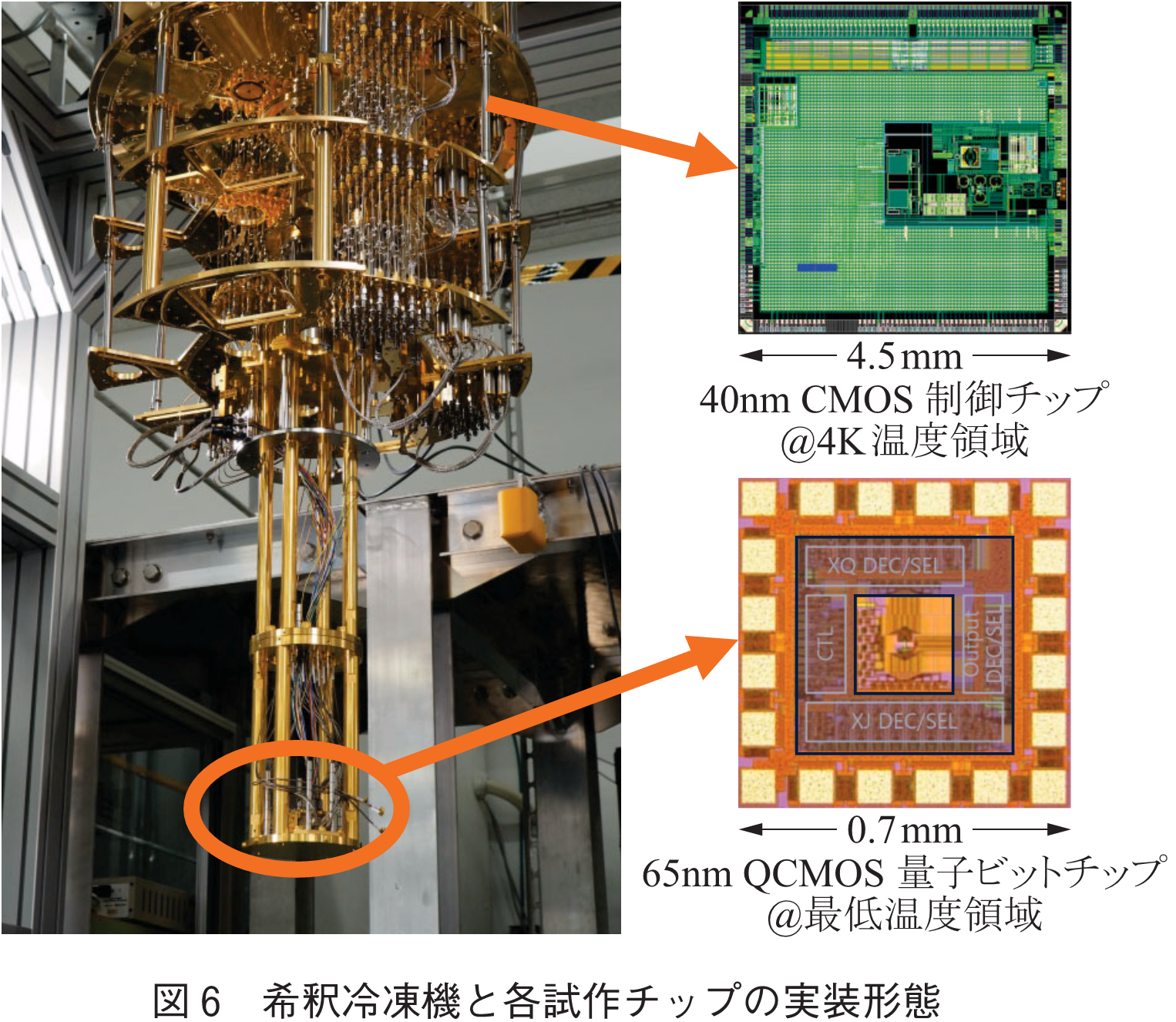

希釈冷凍機はその構造上,4Kまでの冷却は,冷却能力の高い冷却装置が使えるので,その利点を生かし,量子ドットチップから最も近い位置である,4Kプレート上への極低温制御LSI(CAC: Cryogenic Analog Control Chip)の実装を試みている(図6).CACを希釈冷凍機へ搭載する際は,信号線とともに電源配線の確保も必要である.希釈冷凍機への配線は細く抵抗が高いので,電源インピーダンスを低く設定するためには工夫が必要である.最初の試作においては,128量子ビットの実現に向けて,量子ビット部にスイッチマトリックスを搭載し,CACに必要なバイアス電圧発生機能(14)と,量子ビット駆動用のマイクロ波を発生する回路を搭載した構成を念頭に開発を進めた.

我々の提案方式の効果を見積もったところ,CACへの入力信号(6本)及び電源に使用する本数も含めて,4Kプレートにて,ほぼ全ての熱の流入が吸収できることが分かり,制御装置からQBA(Quantum Bit Array Chip)までの熱流入を室温に設置の場合と比較し,CACを用いることで1/20に低減できる見込みが得られた.一方で,信号品質への効果として,室温での信号生成から4Kでの信号生成へ変えることで,熱雑音を20dB削減でき,更に,量子ビットを駆動するためのマイクロ波の強度は,室温に対して4Kでの信号生成による熱雑音低減とともに,室温環境下から流入する熱雑音を削減する目的で挿入されるアッテネータの削減により,-20dBに低電力化できる見込みを得た.このことは逆に考えると,RF信号の発生に回路的な余裕が生まれるので,量子スピン操作(RFの周波数と振幅が重要)に対して優位に働くと考えられる.更に,配線長が削減できるために,信号遅延を1/5に短縮できる見込みである.信号遅延が低減できることは,将来的に,量子エラー訂正を実装する際に高速なフィードバックが期待できるメリットもある.

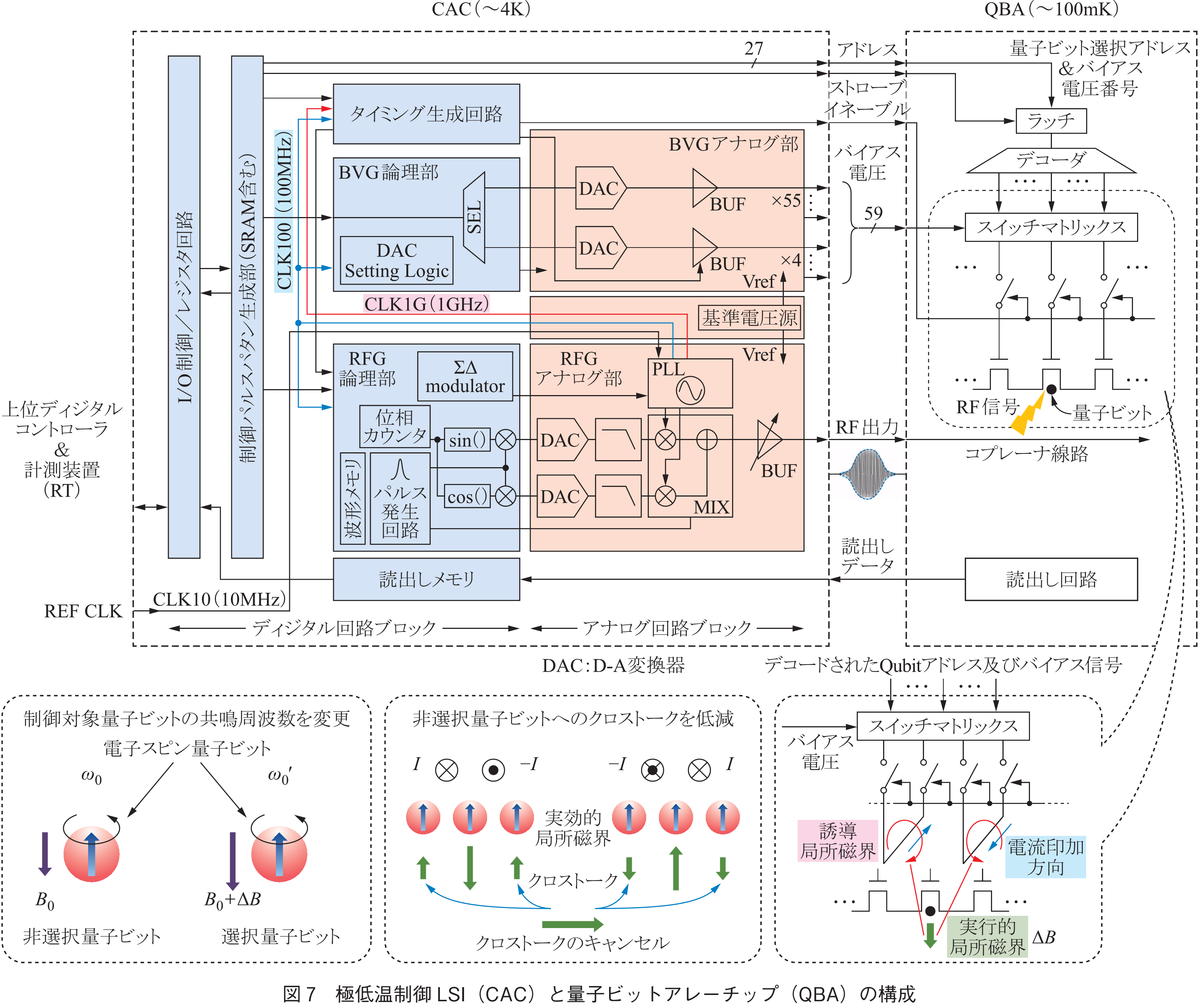

このようなシステムを実現するためのCAC及び,QBAの構成を図7に示す.CACへの制御信号を汎用の少数ビットインタフェースで駆動する方式を採用し,CACは59chバイアス発生回路(BVG: Bias Voltage Generator)(14)及びマイクロ波発生回路(RFG: RF Generator)を搭載している.QBAには,量子ビットを効率的に選択するためのスイッチマトリックスを設け,CACからQBAへの選択信号を効率化するとともに,同図に示すように電流印加も可能な構成とした.QBAへ電流を印加することで,量子ビットに実効的な局所磁界を発生させて,多数ある量子ビットから目的の量子ビットへの選択的な制御を実現させることを目指している.なお,このような局所磁界は,選択量子ビット以外の他の量子ビットへも無視できないクロストーク雑音が載ることが想定される.しかし,最初の電流印加と逆向きの電流を続いて印加することで,その影響が低減できる.このとき,実効的な磁界の大きさが変化するので,選択した量子ビットへの制御用のマイクロ波の周波数を適切に調節する必要がある.

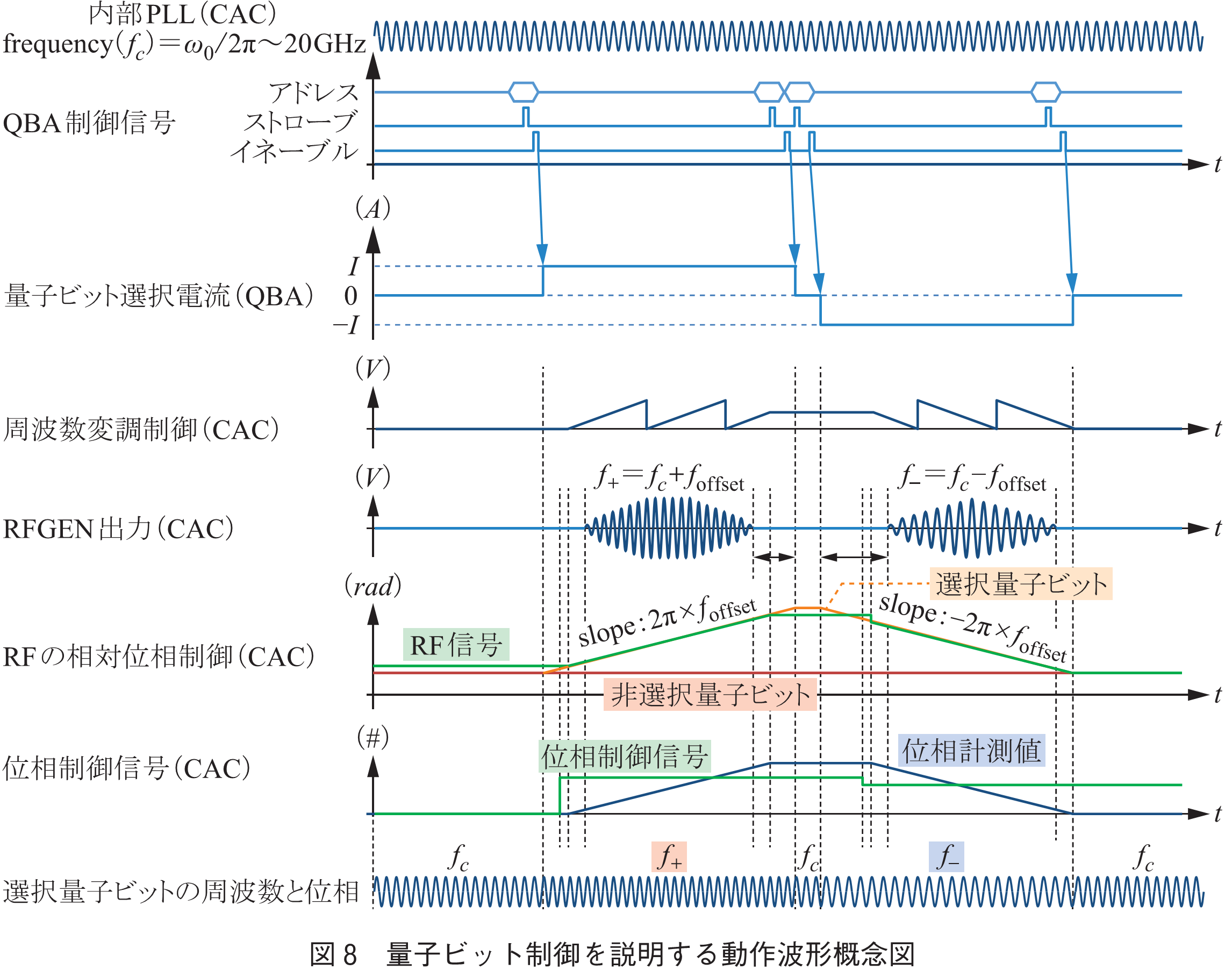

提案方式による量子ビット制御について動作波形図(図8)を用いて説明する.本方式においては,CACの内部クロックを,量子ビットの周波数(静磁界下電子スピンの歳差周波数,この場合20GHz)に設定し,その分周でシステムクロックを動作させる.量子ビットを選択するために,27ビットのアドレス信号(量子ビット選択及びバイアス電圧選択)をQBAに送信し,量子ビットを選択する.指定した量子ビットのゲートに適切な電圧を印加し,選択のための電流を印加して量子ビットの実効的な磁界を変調させ,周波数を調整したマイクロ波を印加する.1回の量子演算を2操作に分け,前半と後半で電流印加方向を逆転させ,マイクロ波の周波数も変更させて制御を実施する.2回のマイクロ波の印加を適切に調整することで,演算終了後の電子スピンの位相を元の状態に戻す.なお,マイクロ波の周波数調整は,三角波を重畳することで実現する.

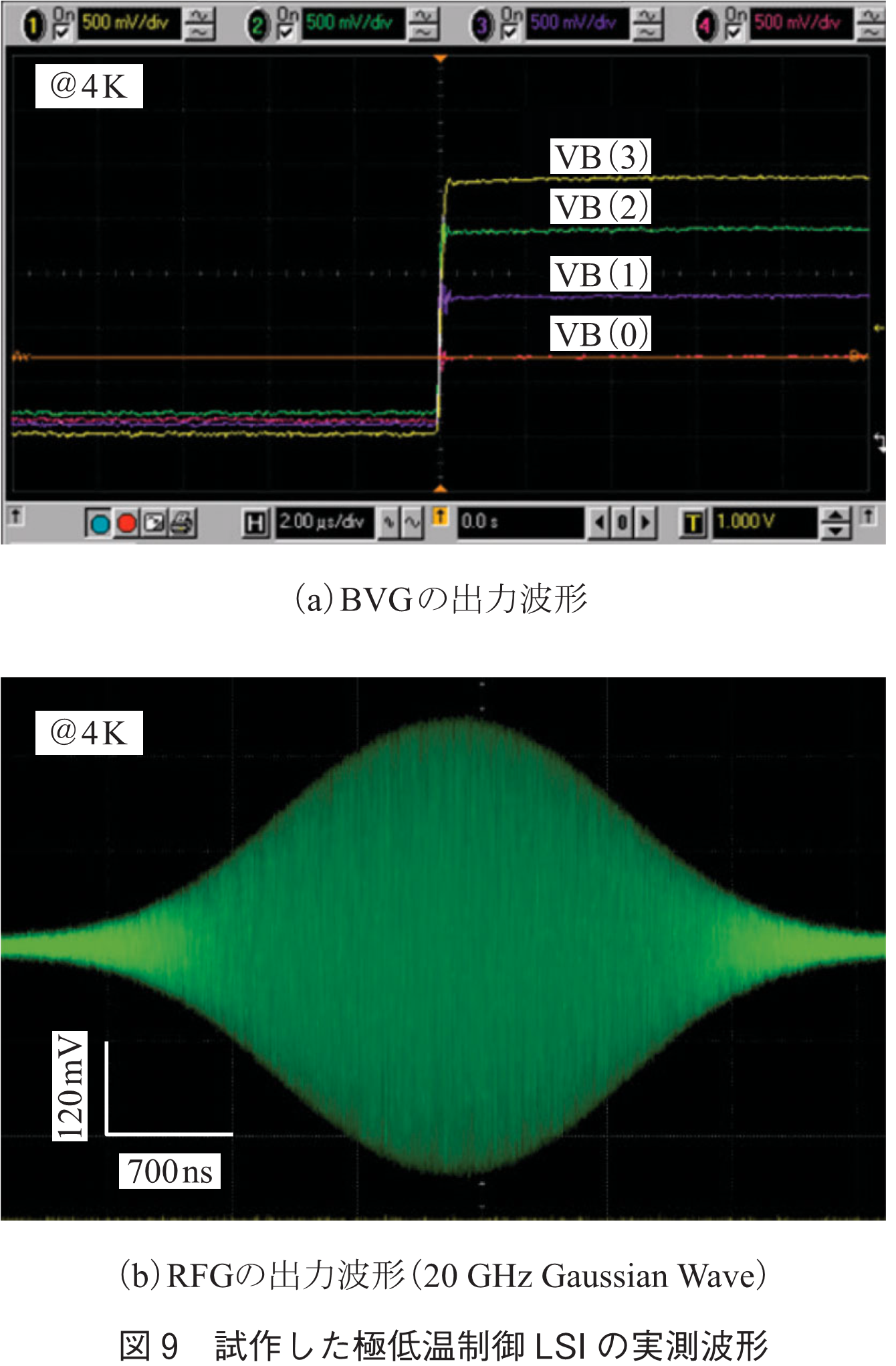

開発したCACの測定結果を図9に示す.バイアス発生回路の特性並びに,20GHzのガウス型包絡線マイクロ波の出力を確認しており,今後,QBAの制御実験へと進む.

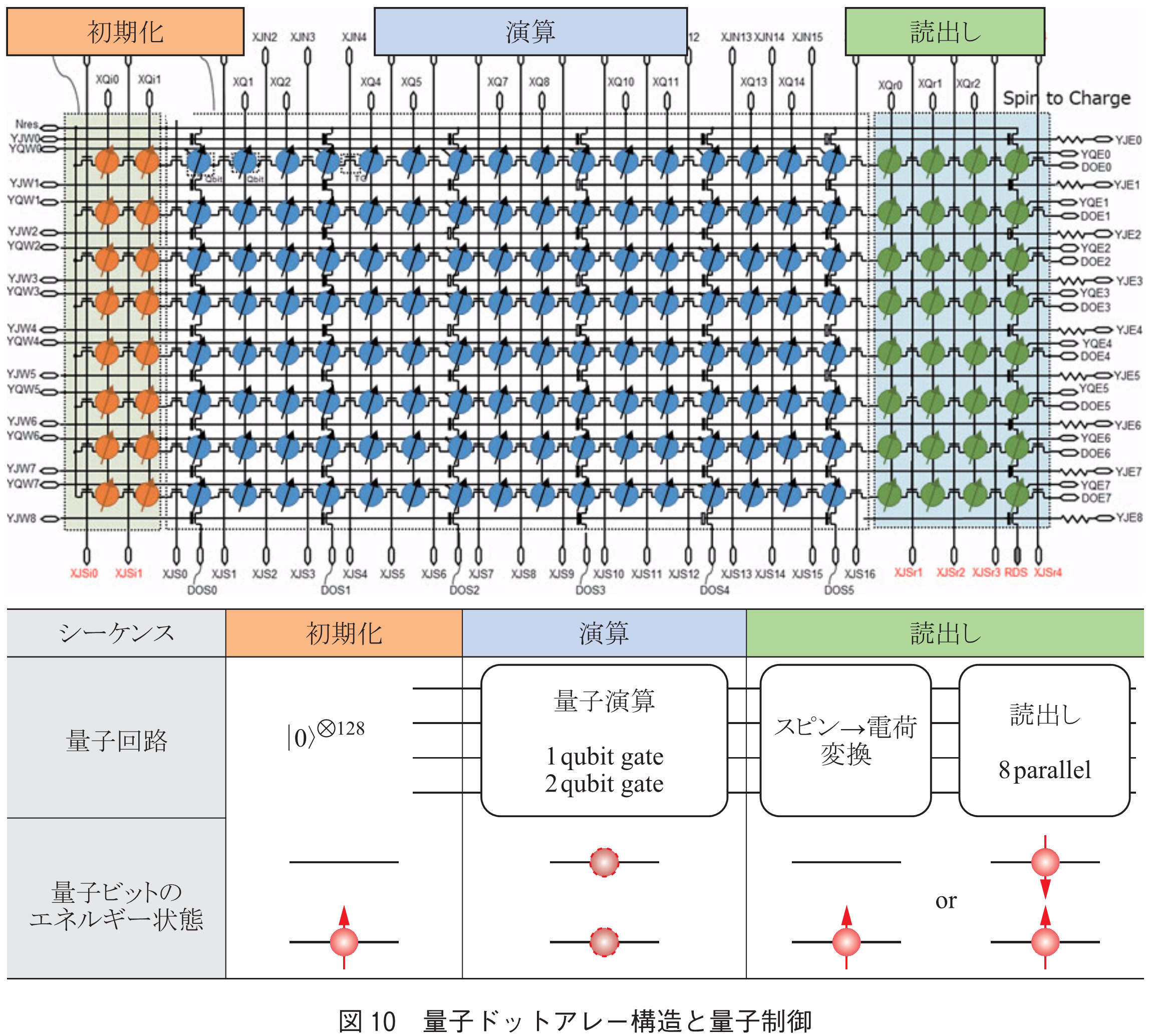

現在開発しているシリコン電子型量子コンピュータは,シリコンの高い集積性を利用し,二次元アレー構造で量子ドットを構成する.量子ドットアレーは,初期化,演算,読出しの,各役割を分けた構造としている(図10).

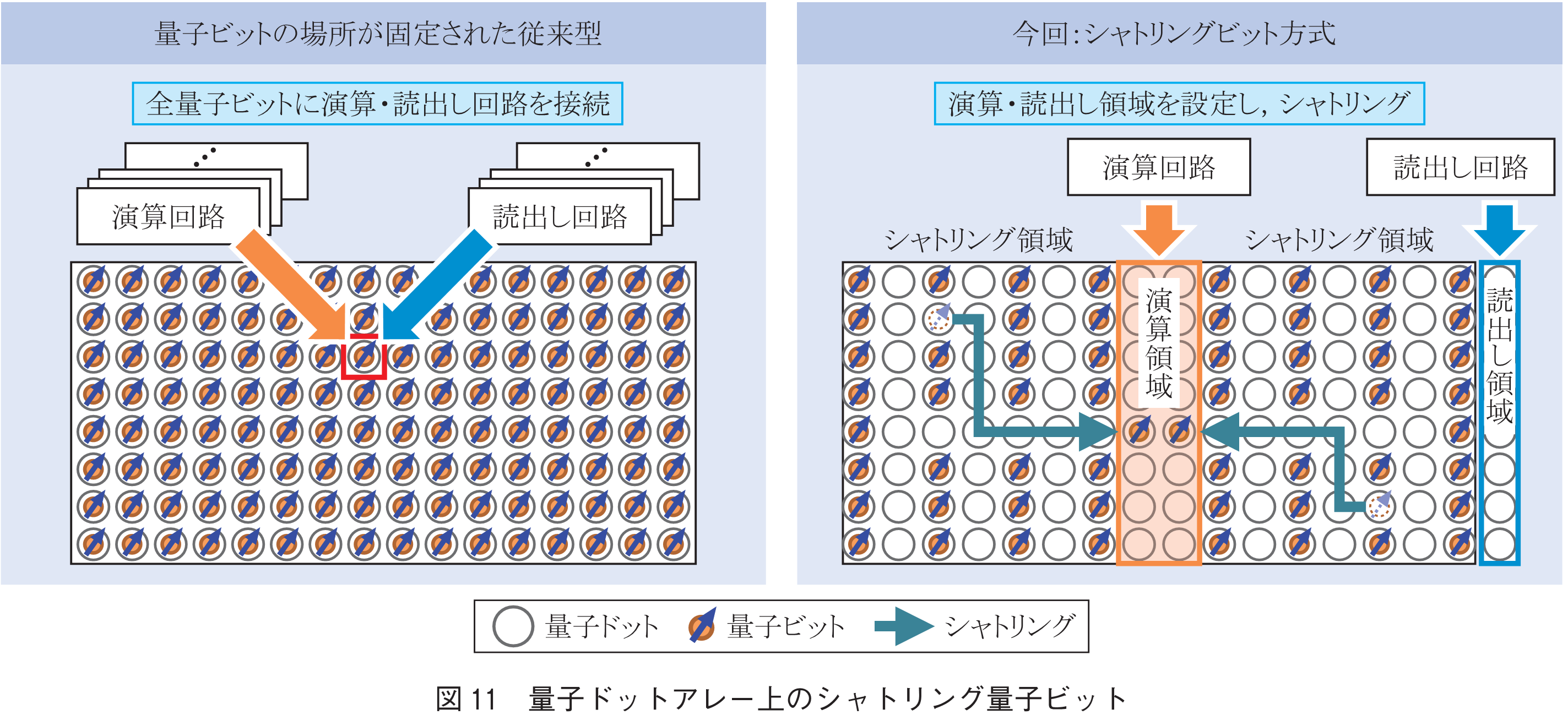

量子ビットの制御方法として,新しく提案している方式は,量子ビットを移動させるシャトリング量子ビット方式である(図11)(7),(15).量子ビット演算にはマイクロ波印加が必要であるが,制御しない量子ビットへもマイクロ波が照射されるため,意図しない量子ビットへの量子操作が生じてしまう(クロストーク).マイクロ波印加の領域をあらかじめ固定し,必要な演算を実施する際に,そのマイクロ波印加領域へ量子ビットを移動させる方式により量子演算の高精度化を実現させるもくろみである.現在,この制御を効率化するための設計ツールや量子OSなどの開発も同時並行して進めている.

量子コンピュータの概説と,シリコン電子スピン型量子コンピュータ開発について述べた.多量子ビットを集積したシリコン量子コンピュータの早期実用化を目指す.

謝辞 本研究の一部は,JSTムーンショット型研究開発事業グラント番号JPMJMS2065の支援を受けたものです.同研究プロジェクトの神戸大学/永田 真教授,東京工業大学/小寺哲夫准教授,米田 淳特任准教授,理化学研究所/中島 峻上級研究員,上記研究機関及び日立製作所の本研究参加者に感謝の意を表します.

(1) https://research.ibm.com/blog/next-wave-quantum-centric-supercomputing

(2) F. Arute, K. Arya, R. Babbush, D. Bacon, J.C. Bardin, R. Barends, R. Biswas, S. Boixo, F.G.S.L. Brandao, D.A. Buell, B. Burkett, Y. Chen, Z. Chen, B. Chiaro, R. Collins, W. Courtney, A. Dunsworth, E. Farhi, B. Foxen, A. Fowler, C. Gidney, M. Giustina, R. Graff, K. Guerin, S. Habegger, M.P. Harrigan, M.J. Hartmann, A. Ho, M. Hoffmann, T. Huang, T.S. Humble, S.V. Isakov, E. Jeffrey, Z. Jiang, D. Kafri, K. Kechedzhi, J. Kelly, P.V. Klimov, S. Knysh, A. Korotkov, F. Kostritsa, D. Landhuis, M. Lindmark, E. Lucero, D. Lyakh, S. Mandrà, J.R. McClean, M. McEwen, A. Megrant, X. Mi, K. Michielsen, M. Mohseni, J. Mutus, O. Naaman, M. Neeley, C. Neill, M.Y. Niu, E. Ostby, A. Petukhov, J.C. Platt, C. Quintana, E.G. Rieffel, P. Roushan, N.C. Rubin, D. Sank, K.J. Satzinger, V. Smelyanskiy, K.J. Sung, M.D. Trevithick, A. Vainsencher, B. Villalonga, T. White, Z.J. Yao, P. Yeh, A. Zalcman, H. Neven, and J.M. Martinis, “Quantum supremacy using a programmable superconducting processor,” Nature, vol.574, pp.505-510, 2019.

(3) https://www.riken.jp/pr/news/2023/20230324_1/index.html

(4) B. Munger, K. Wilcox, J. Sniderman, C. Tung, B. Johnson, R. Schreiber, C. Henrion, K. Gillespie, T. Burd, H. Fair, D. Johnson, J. White, S. McLelland, S. Bakke, J. Olson, R. McCracken, M. Pickett, A. Horiuchi, H. Nguyen, and T.H. Jackson, “Zen 4”: The AMD 5nm 5.7GHz x86-64 microprocessor core,” 2023 IEEE International Solid-State Circuits Conference (ISSCC), pp.38-39, doi: 10.1109/ISSCC42615.2023.10067540, San Francisco, USA, 2023.

(5) R.P. Feynman, “Simulating physics with computers,” Int. J. Theor. Phys., vol.21, pp.467-488, 1982.

(6) J. Preskill, “Quantum computing in the NISQ era and beyond,” Quantum, vol.2, p.79, 2018.

(7) H. Mizuno, “Quantum computing from hype to game changer,” 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), pp.1-4 (Keynote), Kyoto, Japan, 2023.

(8) D. Loss and D.P. DiVincenzo, “Quantum computation with quantum dots,” Phys. Rev. A, vol.57, pp.120-126 Jan. 1998.

(9) N. Lee, R. Tsuchiya, Y. Kanno, T. Mine, Y. Sasago, G. Shinkai, R. Mizokuchi, J. Yoneda, T. Kodera, C. Yoshimura, S. Saito, D. Hisamoto, and H. Mizuno, “16 x 8 quantum dot array operation at cryogenic temperatures,” Jpn. J. Appl. Phys., vol.61, SC1040, 2022.

(10) T. Utsugi, T. Kuno, N. Lee, R. Tsuchiya, T. Mine, D. Hisamoto, S. Saito, and H. Mizuno. “Single-electron routing in a silicon quantum-dot array,” Phys. Rev. B, vol.108, no.23, 235308, 2023.

(11) D. Hisamoto, N. Lee, R. Tsuchiya, T. Mine, T. Utsugi, S. Saito, and H. Mizuno, “Electron charge sensor with hole current operating at cryogenic temperature,” Appl. Phys. Express, vol.16, 036504, 2023.

(12) T. Kuno, T. Utsugi, R. Tsuchiya, N. Lee, T. Mine, I. Yanagi, R. Mizokuchi, J. Yoneda, T. Kodera, T. Nakajima, S. Saito, D. Hisamoto, and H. Mizuno, “Adiabatic electron spin resonance inversion in an FDSOI quantum dot array,” APS March Meeting, 2024.

(13) Y. Kanno, T. Miki, Y. Wachi, T. Norimatsu, T. Sekiguchi, S. Akiyama, N. Kusuno, T. Toba, T. Utsugi, M. Kato, S. Muraoka, M. Maeda, M. Taguchi, R. Takahashi, R. Ukai, T. Tsunoda, T. Ogawa, C. Yoshimura, R. Tsuchiya, M. Nagata, and H. Mizuno, “Hierarchical cryogenic control system for 128-shuttling-qubit Si quantum computer,” Silicon Quantum Electronics Workshiop 2023, T72, Oct. 2023.

(14) T. Miki, “Cryogenic bias voltage control circuits for large scale qubit arrays,” ASP-DAC 2023, 5E-5, Jan. 2023.

(15) T. Sekiguchi, N. Sato, T. Utsugi, N. Lee, A. Miyamoto, T. Tomaru, S. Tanaka, C. Yoshimura, R. Ukai, and H. Mizuno, “A computing architecture using shuttling-qubit for a Si qubit array,” Silicon Quantum Electronics Workshiop 2023, W79, Oct. 2023.

(2024年3月31日受付 2024年4月15日最終受付)

オープンアクセス以外の記事を読みたい方は、以下のリンクより電子情報通信学会の学会誌の購読もしくは学会に入会登録することで読めるようになります。 また、会員になると豊富な豪華特典が付いてきます。

電子情報通信学会 - IEICE会誌はモバイルでお読みいただけます。

電子情報通信学会 - IEICE会誌アプリをダウンロード